MS51

Nov. 28, 2019

Page

450

of 491

Rev 1.00

MS51

32K

SE

RIES

TE

CHNICAL RE

F

EREN

CE MA

N

UAL

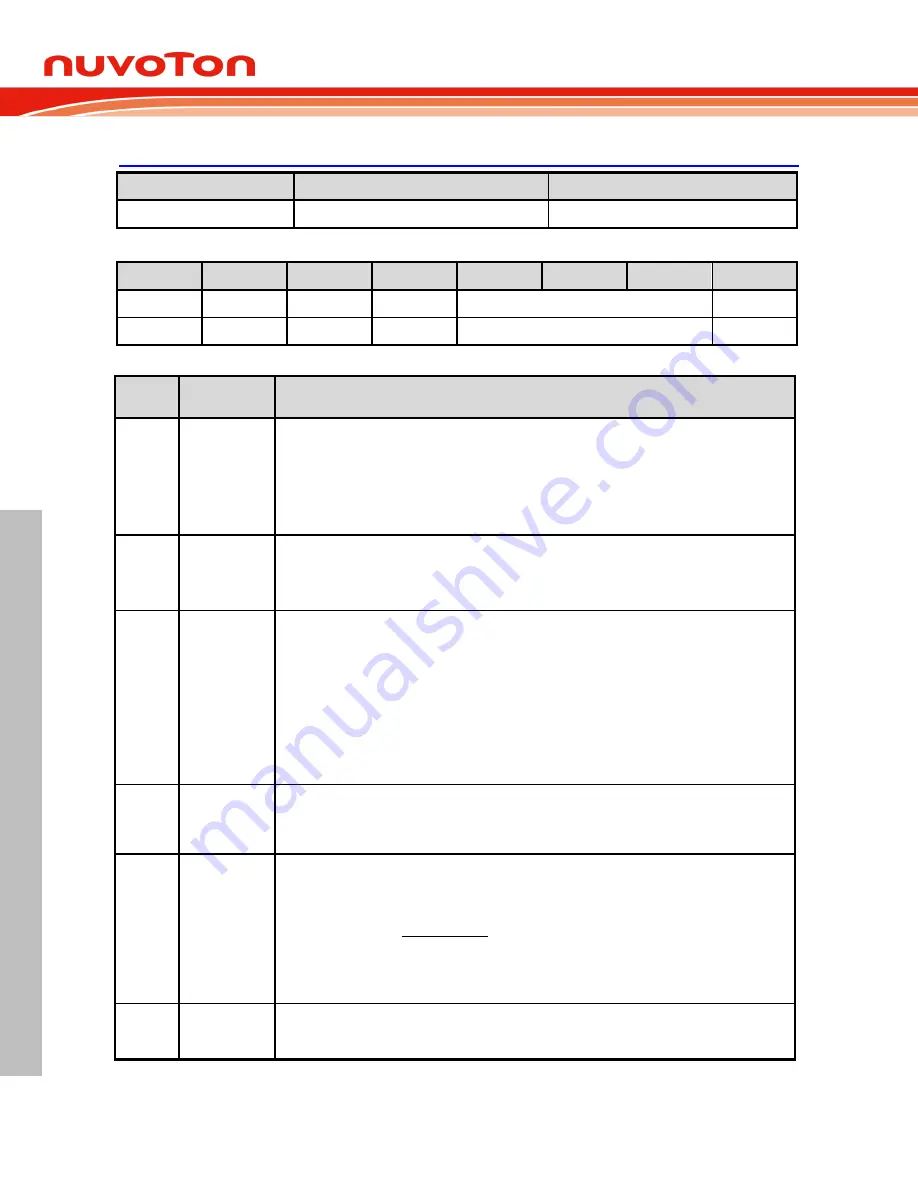

ADCCON2

– ADC Control 2

Register

SFR Address

Reset Value

ADCCON2

E2H, Page 0

0000_0000 b

7

6

5

4

3

2

1

0

ADFBEN

ADCMPOP

ADCMPEN

ADCMPO

ADCAQT0[2:0]

ADCDLY.8

R/W

R/W

R/W

R

R/W

R/W

Bit

Name

Description

7

ADFBEN

ADC compare result asserting Fault Brake enable

0 = ADC asserting Fault Brake Disabled.

1 = ADC asserting Fault Brake Enabled. Fault Brake is asserted once its compare result

ADCMPO is 1. Meanwhile, PWM channels output Fault Brake data. PWMRUN

(PWMnCON0.7) will also be automatically cleared by hardware. The PWM output resumes

when PWMRUN is set again.

6

ADCMPOP

ADC comparator output polarity

0 = ADCMPO is 1 if ADCR[11:0] is greater than or equal to ADCMP[11:0].

1 = ADCMPO is 1 if ADCR[11:0] is less than ADCMP[11:0].

5

ADCMPEN

ADC result comparator enable.

ADC result comparator to trig ADCF enable bit. Only when comparator value match the condition

of ADC compare value defined ADCF will be set to 1. This condition base on ADCMPH,

ADCMPL and ADCMPOP register define.

The ADCF register changes to 1 only when ADC comparing result matches the condition and

then enters interrupt vector if ADC interrupt is enabled.

0 = ADC result comparator trig ADCF Disabled.

1 = ADC result comparator trig ADCF Enabled.

Note

: After this bit is enabled and ADC start is triggered, the ADC keeps converting. The register

ADCRH and ADCRL value will change based on the result of ADC setting and can also be read

out from the register. This process only stops after ADCF is set to 1

4

ADCMPO

ADC comparator output value

This bit is the output value of ADC result comparator based on the setting of ACMPOP. This bit

updates after every A/D conversion complete.

3:1

ADCAQT0[2:0]

ADC acquisition time 1

This 3-bit field decides the acquisition time for ADC AIN0~AIN7 and BG sampling, following by

equation below:

ADC acquisition time =

ADCAQT

F

6

ADCAQT0

*

4

. F

ADCAQT

define is in ADCDIV (ADCCON2[3:1])

The default and minimum acquisition time is 6 ADC clock cycles. Note that this field should not

be changed when ADC is in converting.

0

ADCDLY.8

ADC external trigger delay counter bit 8

See ADCDLY register.