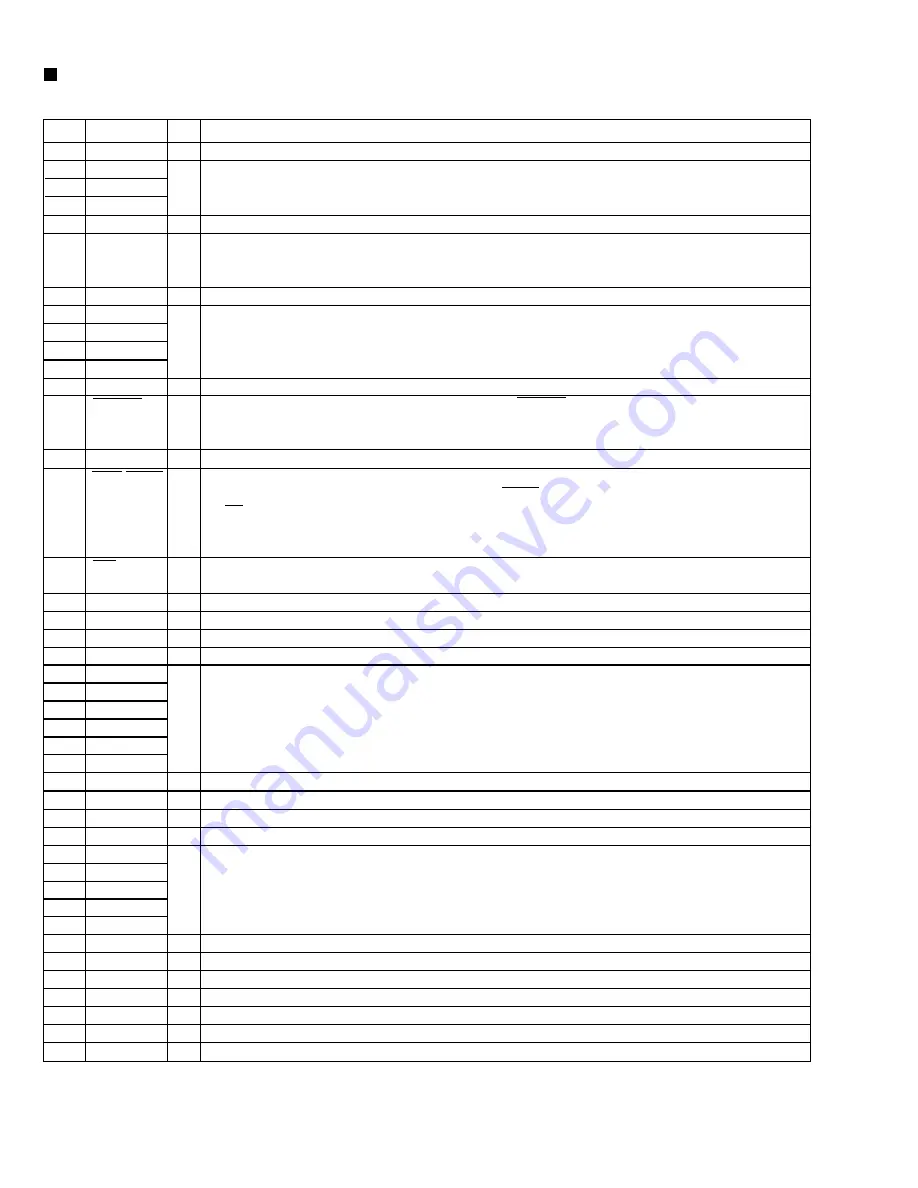

TH-A9

1-36

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

PIO0

HDATA0

HDATA1

HDATA2

VDD-3.3

HDATA3

VSS

HDATA4

HDATA5

HDATA6

HDATA7

VDD-2.5

RESET

VSS

WAIT/DTACK

INT

VDD-3.3

NC

VSS

NC

PIO11

PIO12

PIO13

PIO14

PIO15

PIO16

VDD-3.3

PIO17

VSS

PIO18

PIO19

PIO20

PIO21

PIO22

PIO23

VDD-3.3

PIO24

VSS

PIO25

VDD-2.5

PIO26

VSS

Pin No.

Symbol

I/O

I/O

-

I/O

-

I/O

-

I

-

O

O

-

O

-

O

I/O

-

I/O

-

I/O

I/O

-

I/O

-

I/O

-

I/O

-

I/O

Function

ZIVA3-PE0 (IC501) : AV Decoder

ZIVA3-PEO (1/5)

1. Terminal Description

Programmable I/O pin, which enters input mode after resetting.

8-bit, bi-directional host data bus. Write data in decoder Code FIFO via HDATA.

The 32-bit word MSB is written first. The host reads and writes the internal register of

the decoder and local SRAM via HDATA.

3.3 V supply voltage for I/O signals.

8-bit, bi-directional host data bus. Writes data in decoder Code FIFO via HDATA.

The 32-bit word MSB is written first. The host reads and writes the internal register of

the decoder and local SRAM via HDATA.

Core logic and I/O signal grounding.

8-bit, bi-directional host data bus. Write data in decoder Code FIFO via HDATA.

The 32-bit word MSB is written first. The host reads and writes the internal register of

the decoder and local SRAM via HDATA.

2.5 V supply voltage for the core logic.

Hardware reset. An external device expresses RESET (Active Low) to execute hardware

resetting of the decoder. RESET is expressed for at least 20 ms to guarantee optimum

initialization to occur after power has stabilized.

Core logic and I/O signal grounding.

Transfer incomplete/data acknowledgement, which is an Active Low signal indicating that

transfer started by the host is not completed. WAIT is expressed after negative going edge

of CS, and expressed again when the decoder is ready for completing the transfer cycle.

As the signal for opening the drain should be pulled up from 1 V to 3.3 V, it is driven at

high speed for 10 ns before the tri-state condition is entered.

Host interrupt. As the signal for opening the drain should be pulled up from 4.7 V to 3.3 V,

it is driven at high speed for 10 ns before the tri-state condition is entered.

3.3 V supply voltage for I/O signals.

No connection.

Core logic and I/O signal grounding.

No connection.

Programmable I/O pins, which enter input mode. after resetting.

3.3 V supply voltage for I/O signals.

Programmable I/O pin, which enters input mode after resetting.

Core logic and I/O signal grounding.

Programmable I/O pin, which enters input mode after

Programmable I/O pins, which enter output mode after resetting.

3.3 V supply voltage for I/O signals.

Programmable I/O pin, which enters output mode after resetting.

Core logic and I/O signal grounding.

Programmable I/O pin, which enters output mode after resetting.

2.5 V supply voltage for the core logic.

Programmable I/O pin, which enters output mode after resetting.

Core logic and I/O signal grounding.