16 I

2

C (I2C)

S1C31D50/D51 TECHNICAL MANUAL

Seiko Epson Corporation

16-7

(Rev. 2.00)

Data transmission using DMA

By setting the I2C_

n

TBEDMAEN.TBEDMAEN

x

bit to 1 (DMA transfer request enabled), a DMA transfer

request is sent to the DMA controller and transmit data is transferred from the specified memory to the I2C_

n

TXD register via DMA Ch.

x

when the I2C_

n

INTF.TBEIF bit is set to 1 (transmit buffer empty).

This automates the data sending procedure from Steps 5, 6, and 8 described above.

The transfer source/destination and control data must be set for the DMA controller and the relevant DMA

channel must be enabled to start a DMA transfer in advance so that transmit data will be transferred to the I2C_

n

TXD register. For more information on DMA, refer to the “DMA Controller” chapter.

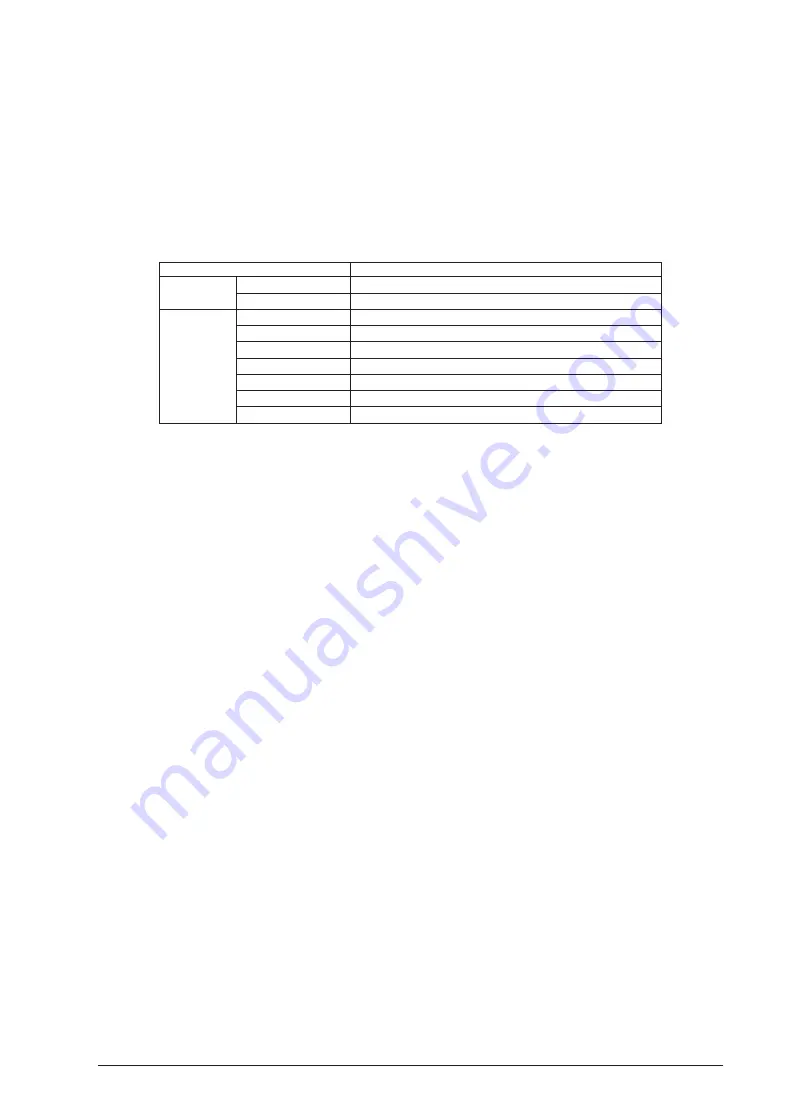

Table 16.4.2.1 DMA Data Structure Configuration Example (for Data Transmission)

Item

Setting example

End pointer Transfer source

Memory address in which the last transmit data is stored

Transfer destination I2C_nTXD register address

Control data dst_inc

0x3 (no increment)

dst_size

0x0 (byte)

src_inc

0x0 (+1)

src_size

0x0 (byte)

R_power

0x0 (arbitrated for every transfer)

n_minus_1

Number of transfer data

cycle_ctrl

0x1 (basic transfer)

16.4.3 Data Reception in Master Mode

A data receiving procedure in master mode and the I2C Ch.

n

operations are shown below. Figures 16.4.3.1 and

16.4.3.2 show an operation example and a flowchart, respectively.

Data receiving procedure

1. Issue a START condition by setting the I2C_

n

CTL.TXSTART bit to 1.

2. Wait for a transmit buffer empty interrupt (I2C_

n

INTF.TBEIF bit = 1) or a START condition interrupt (I2C_

n

INTF.STARTIF bit = 1).

Clear the I2C_

n

INTF.STARTIF bit by writing 1 after the interrupt has occurred.

3. Write the 7-bit slave address to the I2C_

n

TXD.TXD[7:1] bits and 1 that represents READ as the data trans-

fer direction to the I2C_

n

TXD.TXD0 bit.

4. (When DMA is used) Configure the DMA controller and set a DMA transfer request enable bit in the I2C_

n

RBFDMAEN register to 1 (DMA transfer request enabled). (This automates the data receiving procedure

Steps 5, 7, and 9.)

5. (When DMA is not used) Wait for a receive buffer full interrupt (I2C_

n

INTF.RBFIF bit = 1) generated

when a one-byte reception has completed.

6. Perform one of the operations below when the last or next-to-last data is received.

i. When the next-to-last data is received, write 1 to the I2C_

n

CTL.TXNACK bit to send a NACK after the

last data is received, and then go to Step 7.

ii. When the last data is received, read the received data from the I2C_

n

RXD register and set the I2C_

n

CTL.TXSTOP to 1 to generate a STOP condition. Then go to Step 10.

7. (When DMA is not used) Read the received data from the I2C_

n

RXD register.

8

.

If a NACK reception interrupt (I2C_

n

INTF.NACKIF bit = 1) has occurred, clear the I2C_

n

INTF.NACKIF

bit and issue a STOP condition by setting the I2C_

n

CTL.TXSTOP bit to 1. Then go to Step 10 or Step 1 if

making a retry.

9. (When DMA is not used) Repeat Steps 5 to 7 until the end of data reception.

10. Wait for a STOP condition interrupt (I2C_

n

INTF.STOPIF bit = 1).

Clear the I2C_

n

INTF.STOPIF bit by writing 1 after the interrupt has occurred.