2 POWER SUPPLY, RESET, AND CLOCKS

S1C31D50/D51 TECHNICAL MANUAL

Seiko Epson Corporation

2-13

(Rev. 2.00)

OSC1 oscillation stop detection function

The oscillation stop detection function restarts the OSC1 oscillator circuit when it detects oscillation stop under

adverse environments that may stop the oscillation. Follow the procedure shown below to enable the oscillation

stop detection function.

1. After enabling the OSC1 oscillation, check if the stabilized clock is supplied (CLGINTF.OSC1STAIF bit = 1).

2. Write 1 to the CLGINTF.OSC1STPIF bit.

(Clear interrupt flag)

3. Write 1 to the CLGINTE.OSC1STPIE bit.

(Enable interrupt)

4. Write 0x0096 to the SYSPROT.PROT[15:0] bits. (Remove system protection)

5. Set the following CLGOSC1 register bits:

- Set the CLGOSC1.OSDRB bit to 1.

(Enable OSC1 restart function)

- Set the CLGOSC1.OSDEN bit to 1.

(Enable oscillation stop detection function)

6. Write a value other than 0x0096 to the SYSPROT.PROT[15:0] bits. (Set system protection)

7. The OSC1 oscillation stops if the CLGINTF.OSC1STPIF bit = 1 after an interrupt occurs.

If the CLGOSC1.OSDRB bit = 1, the hardware restarts the OSC1 oscillator circuit.

Note: Enabling the oscillation stop detection function increase the oscillation stop detector current (I

OSD1

).

2.4 Operating Mode

2.4.1 Initial Boot Sequence

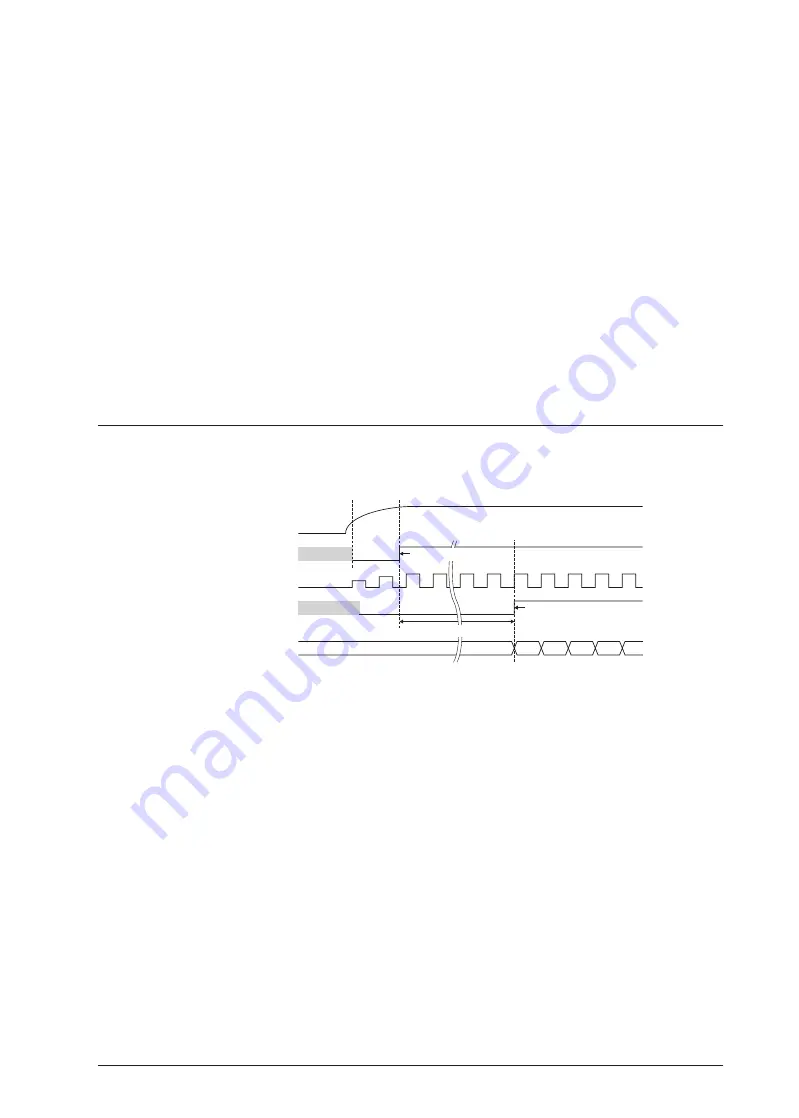

Figure 2.4.1.1 shows the initial boot sequence after power is turned on.

V

DD

Reset request from POR

IOSCCLK

(Initial SYSCLK)

Internal reset signal

SYSRST, H0, H1

Cortex

®

-M0+ core

program counter (PC)

Cancel reset request

Undefined

Undefined

∗

1

∗

1: Reset vector (reset handler start address)

∗

2: Address (reset 2)

∗

2

Cancel reset request

Reset hold time t

RSTR

Figure 2.4.1.1 Initial Boot Sequence

Note: The reset cancelation time at power-on varies according to the power rise time and reset request

cancelation time.

For the reset hold time t

RSTR

, refer to “Reset hold circuit characteristics” in the “Electrical Characteristics” chapter.

2.4.2 Transition between Operating Modes

State transitions between operating modes shown in Figure 2.4.2.1 take place in this IC.

RUN mode

RUN mode refers to the state in which the CPU is executing the program. A transition to this mode takes place

when the system reset request from the system reset controller is canceled. RUN mode is classified into “IOSC

RUN,” “OSC1 RUN,” “OSC3 RUN,” and “EXOSC RUN” by the SYSCLK clock source.

HALT mode

When the Cortex

®

-M0+ core executes the WFI or WFE instruction with the SLEEPDEEP bit of the system con-

trol register set to 0, it suspends program execution and stops operating. This state is referred to HALT mode in

this IC. In this mode, the clock sources and peripheral circuits keep operating. This mode can be set while no

software processing is required and it reduces power consumption as compared with RUN mode. HALT mode

is classified into “IOSC HALT,” “OSC1 HALT,” “OSC3 HALT,” and “EXOSC HALT” by the SYSCLK clock

source.