62

CY8C28xxx PSoC Programmable System-on-Chip TRM, Document No. 001-52594 Rev. *G

RAM Paging

4.2.6

MVW_PP Register

The MVI Write Page Pointer Register (MVW_PP) is used to

set the effective SRAM page for MVI write memory

accesses in a multi-SRAM page PSoC device.

Bits 2 to 0: Page Bits[2:0].

These bits are only used by the

MVI [expr], A instruction, not to be confused with the MVI A,

[expr] instruction covered by the MVR_PP register. This

instruction is considered a write because data is transferred

from the microprocessor's A register (CPU_A) to SRAM.

When an MVI [expr], A instruction is executed in a device

with more than one page of SRAM, the SRAM address that

is written by the instruction is determined by the value of the

least significant bits in this register. However, the pointer for

the MVI [expr], A instruction is always located in the current

SRAM page. See the

PSoC Designer Assembly Language

User Guide

for more information on the MVI [expr], A

instruction.

The function of this register and the MVI instructions are

independent of the SRAM Paging bits in the CPU_F register.

For additional information, refer to the

.

4.2.7

CPU_F Register

The M8C Flag Register (CPU_F) provides read access to

the M8C flags.

Bits 7 and 6: PgMode[1:0].

PgMode determines how the

CUR_PP and IDX_PP registers are used in forming effective

RAM addresses for Direct Address mode and Indexed

Address mode operands.

Bit 4: XIO.

The I/O Bank Select bit, also know as the regis-

ter bank select bit, is used to select the register bank that is

active for a register read or write. This bit allows the PSoC

device to have 512 8-bit registers and therefore, can be

thought of as the ninth address bit for registers. The address

space accessed when the XIO bit is set to ‘0’ is called the

, while the address space accessed when the

XIO bit is set to ‘1’ is called the

Bit 2: Carry.

The Carry Flag bit is set or cleared in

response to the result of several instructions. It can also be

manipulated by the flag-logic opcodes (for example,

OR F, 4). See the

PSoC Designer Assembly Guide User

Manual

for more details.

Bit 1: Zero.

The Zero Flag bit is set or cleared in response

to the result of several instructions. It can also be manipu-

lated by the flag-logic opcodes (for exam

4.2.8

MVR_PP Register

The MVI Read Page Pointer Register (MVR_PP) is used to

set the effective SRAM page for MVI read memory accesses

in a multi-SRAM page PSoC device.

Bits 2 to 0: Page Bits[2:0].

These bits are only used by the

MVI A, [expr] instruction, not to be confused with the MVI

[expr], A instruction covered by the MVW_PP register. This

instruction is considered a read because data is transferred

from SRAM to the microprocessor's A register (CPU_A).

When an MVI A, [expr] instruction is executed in a device

with more than one page of SRAM, the SRAM address that

is read by the instruction is determined by the value of the

least significant bits in this register. However, the pointer for

the MVI A, [expr] instruction is always located in the current

SRAM page. See the

PSoC Designer Assembly Language

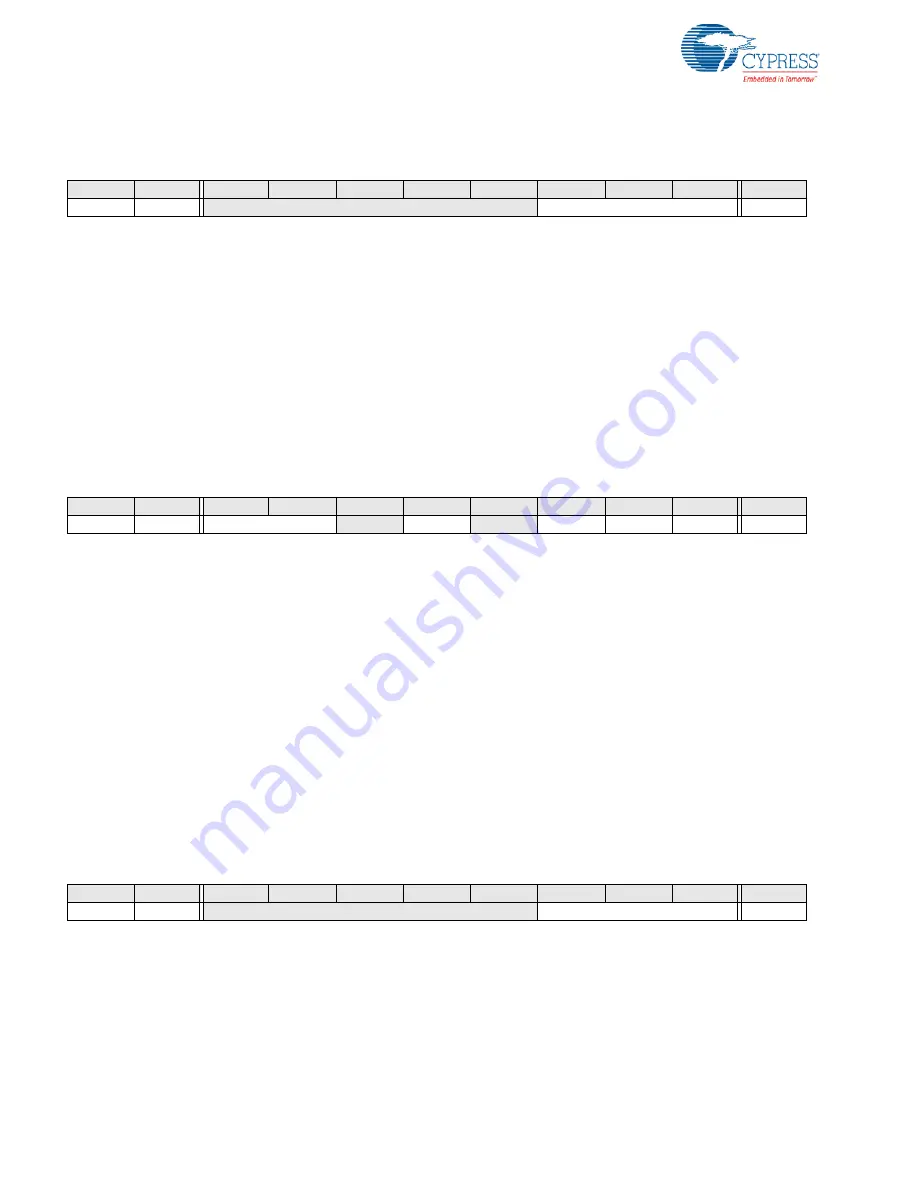

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Access

0,D5h

Page Bits[2:0]

RW : 00

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Access

x,F7h

PgMode[1:0]

XIO

Carry

Zero

GIE

RL : 02

LEGEND

L

The AND F, expr; OR F, expr; and XOR F, expr flag instructions can be used to modify this register.

x

An ‘x’ before the comma in the address field indicates that this register can be read or written to no matter what bank is used.

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Access

0,D4h

Page Bits[2:0]

RW : 00

Содержание CY8C28 series

Страница 65: ...64 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G RAM Paging ...

Страница 85: ...84 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Internal Main Oscillator IMO ...

Страница 93: ...92 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G External Crystal Oscillator ECO ...

Страница 97: ...96 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Phase Locked Loop PLL ...

Страница 125: ...124 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Страница 311: ...310 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G IDAC_CR0 1 FDh ...

Страница 317: ...316 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Страница 393: ...392 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Страница 425: ...424 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Analog Reference ...

Страница 461: ...460 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Two Column Limited Analog System ...

Страница 477: ...476 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Digital Clocks ...

Страница 483: ...482 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Multiply Accumulate MAC ...

Страница 513: ...512 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Internal Voltage Reference ...

Страница 523: ...522 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Switch Mode Pump SMP ...

Страница 533: ...532 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G I O Analog Multiplexer ...

Страница 537: ...536 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Real Time Clock RTC ...

Страница 561: ...560 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...