CY8C28xxx PSoC Programmable System-on-Chip TRM, Document No. 001-52594 Rev. *G

337

Digital Blocks

17.1.2.1

Clock Resynchronization Summary

■

Digital PSoC blocks have extremely flexible clocking

configurations. To maintain reliable timing, input clocks

must be resynchronized.

■

The master clock for any clock in the system is either

SYSCLK or SYSCLKX2. Determine the master clock for

a given input clock and resynchronize to that clock.

■

Do not use divide by 1 clocks derived from SYSCLK and

SYSCLKX2. Use the direct SYSCLK or SYSCLKX2

clocking option available at the block.

17.1.3

Output Demultiplexers

Most functions have two outputs: a primary and an auxiliary

output, the meaning of which are function dependent. Each

of these outputs may be driven onto the row output bus.

Each demux is implemented with four tri-state drivers. There

are two bits in the output register to select one of the four tri-

state drivers and an additional bit to enable the selected

driver.

17.1.4

Block Chaining Signals

Each digital block has the capability to be chained and to

create functions with bit widths greater than eight. There are

signals to propagate information, such as Compare, Carry,

Enable, Capture and Gate, from one block to the next to

implement higher precision functions. The selection made in

the function register determines which signals are appropri-

ate for the desired function. User Modules that have been

designed to implement digital functions, with greater than 8-

bit width, will automatically make the proper selections of the

chaining signals, to ensure the correct information flow

between blocks.

17.1.5

Input Data Synchronization

Any asynchronous input derived from an external source,

such as a GPIO pin input, must be resynchronized through

the row input before use into any digital block clock or data

input. This is the default mode of operation (resynchroniza-

tion is on).

17.1.6

Timer Function

A timer consists of a period register, a

down

counter, and a capture/compare register, all of which are

byte wide. When the timer is disabled and a period value is

written into DR1, the period value is also loaded into DR0.

When the timer is enabled, the counter counts down until

positive terminal count (a count of 00h) is reached. On the

next clock edge, the period is reloaded and, on subsequent

clocks, counting continues. The terminal count signal is the

primary function output. (Refer to the timing diagram for this

function on page

.) This can be configured as a full or

half clock cycle.

This function also supports multi-shot mode. When the

multi-shot register is set to non-zero, the function is in multi-

shot mode. For example, if the multi-shot register is set to

01h, the function is disabled after it reaches the first 00

value in DR0. If the multi-shot register is set to 02h, when

the function reaches the first 00, DR0 is reloaded and runs

again. The function is disabled after the second 00 in DR0

register. The multi-shot supports up to a MAX number of 15

shots.

Hardware capture occurs on the positive edge of the data

input. This event transfers the current count from DR0 to

DR2. The captured value may then be read directly from

DR2. A software capture function is equivalent to a hard-

ware capture. A CPU read of DR0, with the timer enabled,

triggers the same capture mechanism. The hardware and

software capture mechanisms are ORed in the capture cir-

cuitry. Because the capture circuitry is positive edge sensi-

tive, during an interval where the hardware capture input is

high, a software capture is masked and will not occur.

The timer also implements a compare function between

DR0 and DR2. The compare signal is the auxiliary function

output. A limitation, in regards to the compare function, is

that the capture and compare function both use the same

register (DR2). Therefore, if a capture event occurs, it will

overwrite the compare value.

There is another mode, called NPS mode, supported at the

compare output. When it is set, the compare output is

delayed half clock cycle. It is used to achieve a higher reso-

lution when 48MHz clock is used as block clock.

This function also supports KILL function. There are two

KILL modes: KILL-Disable and KILL-Reload. In KILL-Dis-

able mode, the function is disabled immediately when kill is

asserted. The function must be restarted in firmware. In

KILL-Reload mode, the DR0 register and multi-shot counter

register stays in reload state when KILL is high, and the

function counts down when KILL is released. The function

outputs are gated to zeros when KILL is asserted. For more

detail see

Mode bit 1 in the function register sets the compare type

(DR0 <= DR2 or DR0 < DR2) and Mode bit 0 sets the inter-

rupt type (Terminal Count or Compare). There are also two

more bits used to control interrupts, located at bit 1 in CR0

and bit 0 in CR1.

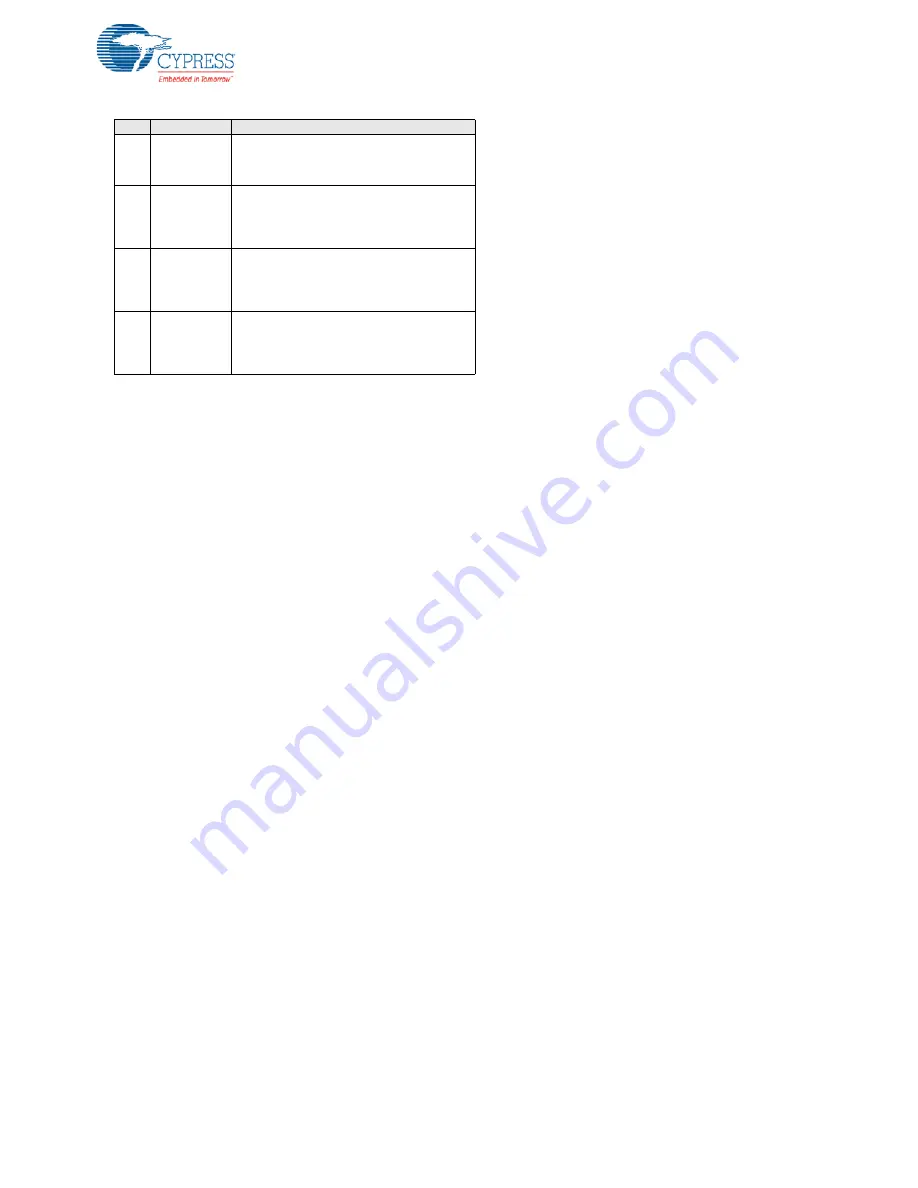

Table 17-1. AUXCLK Bit Selections

Code

Description

Usage

00

Bypass

Use this setting only when SYSCLKX2 (48 MHz) is

selected. Other than this case, asynchronous clock

inputs are not recommended. This setting is also

required for blocks to remain active while in sleep.

01

Resynchronize

to SYSCLK

(24 MHz)

Use this setting for any SYSCLK-based clock. VC1,

VC2, VC3 driven by SYSCLK, digital blocks with

SYSCLK-based source clocks, broadcast bus with

source based on SYSCLK, row input and row out-

puts with source based on SYSCLK.

10

Resynchronize

to SYSCLKX2

(48 MHz)

Use this setting for any SYSCLKX2-based clock.

VC3 driven by SYSCLKX2, digital blocks with

SYSCLKX2-based source clocks, broadcast bus

with source based on SYSCLKX2, row input and

row outputs with source based. on SYSCLKX2.

11

SYSCLK Direct

Use this setting to clock the block directly using

SYSCLK. Note that this setting is not strictly related

to clock resynchronization; because YSCLK cannot

resynchronize itself, it allows a direct skew con-

trolled SYSCLK source.

Содержание CY8C28 series

Страница 65: ...64 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G RAM Paging ...

Страница 85: ...84 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Internal Main Oscillator IMO ...

Страница 93: ...92 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G External Crystal Oscillator ECO ...

Страница 97: ...96 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Phase Locked Loop PLL ...

Страница 125: ...124 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Страница 311: ...310 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G IDAC_CR0 1 FDh ...

Страница 317: ...316 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Страница 393: ...392 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Страница 425: ...424 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Analog Reference ...

Страница 461: ...460 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Two Column Limited Analog System ...

Страница 477: ...476 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Digital Clocks ...

Страница 483: ...482 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Multiply Accumulate MAC ...

Страница 513: ...512 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Internal Voltage Reference ...

Страница 523: ...522 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Switch Mode Pump SMP ...

Страница 533: ...532 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G I O Analog Multiplexer ...

Страница 537: ...536 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Real Time Clock RTC ...

Страница 561: ...560 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...