CY8C28xxx PSoC Programmable System-on-Chip TRM, Document No. 001-52594 Rev. *G

499

I

2

C

Bits 3 and 2: Clock Rate[1:0].

These bits offer a selection

of three sampling and bit rates. All block clocking is based

on the SYSCLK input, which is nominally 24 MHz (unless

the PSoC device is in external clocking mode). The sam-

pling rate and the baud rate are determined as follows:

■

Sample Rate = SYSCLK/Pre-scale Factor

■

Baud Rate = 1/(Sample Rate x Samples per Bit)

The nominal values, when using the internal 24 MHz oscilla-

tor, are shown in

When clocking the input with a frequency other than 24 MHz

(for example, clocking the PSOC device with an external

clock), the baud rates and sampling rates will scale accord-

ingly. Whether the block will work in a Standard Mode or

Fast Mode system depends on the sample rate. The sample

rate must be sufficient to resolve bus events, such as Start

and Stop conditions. (See the

2

C-bus™ Specification

and User Manual, version 03

, for minimum Start and Stop

hold times.)

Bit 1: Enable Master.

When this bit is set, the Master Sta-

tus and Control register is enabled (otherwise it is held in

reset) and I

2

C transfers can be initiated in Master mode.

When the master is enabled and operating, the block will

clock the I

2

C bus at one of three baud rates, defined in the

Clock Rate register. When operating in Master mode, the

hardware is multi-master capable, implementing both clock

synchronization and arbitration. If the Slave Enable bit is not

set, the block will operate in Master Only mode. All external

Start conditions are ignored (although the Bus Busy status

bit will still keep track of bus activity). Block enable will be

synchronized to the SYSCLK clock input (

).

Bit 0: Enable Slave.

When the slave is enabled, the block

generates an interrupt on any Start condition and an

address byte that it receives, indicating the beginning of an

I

2

C transfer. When operating as a slave, the block is clocked

from an external master. Therefore, the block will work at

any frequency up to the maximum defined by the currently

selected clock rate. The internal clock is only used in Slave

mode, to ensure that there is adequate setup time from data

output to the next clock on the release of a slave stall. When

the Enable Slave and Enable Master bits are both ‘0’, the

block is held in reset and all status is cleared. See

for a description of the interaction between the

Master/Slave Enable bits. Block enable will be synchronized

to the SYSCLK clock input (

For additional information, refer to the

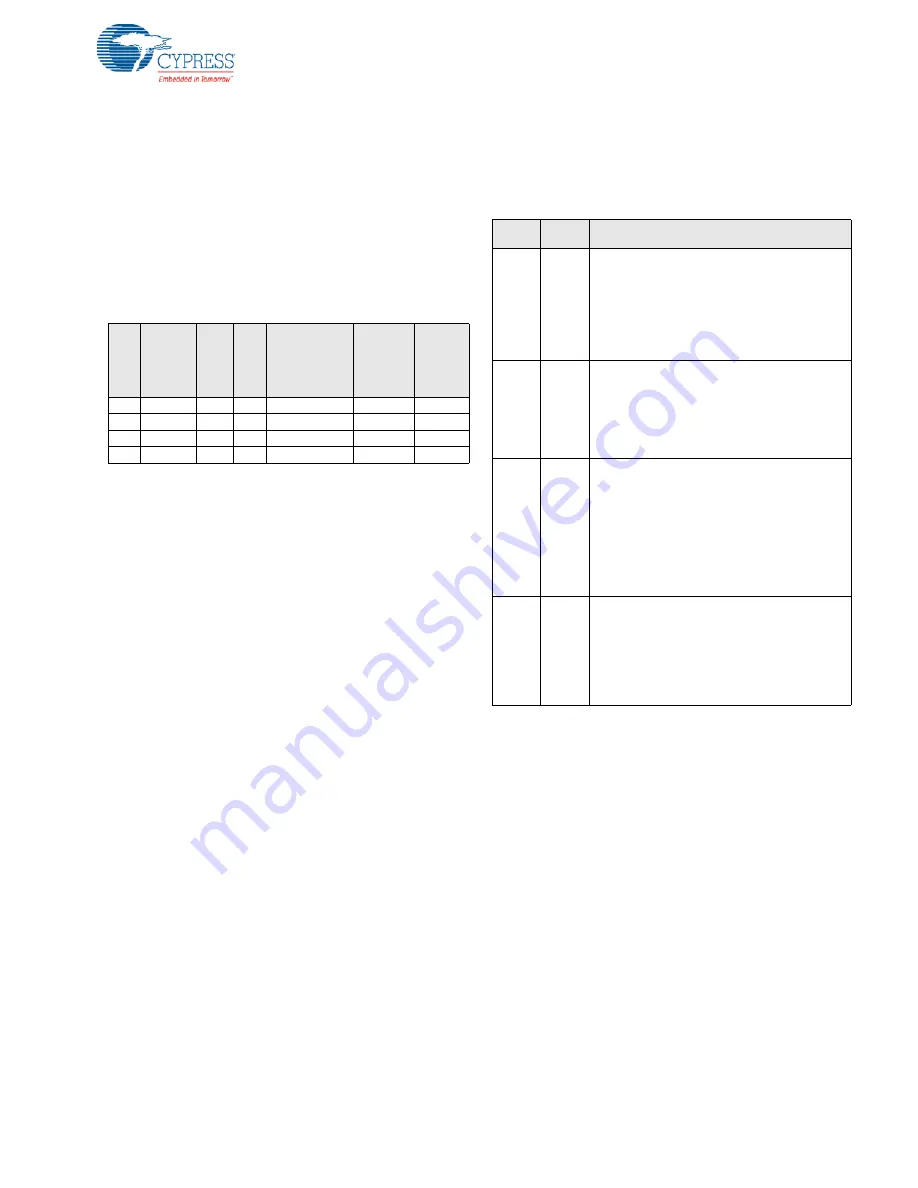

Table 28-3. I

2

C Clock Rates

Clo

c

k Ra

te

[1:0

]

I

2

C Mod

e

S

YSCLK

Pr

e-s

cal

e

Fact

o

r

Sam

p

le

s

pe

r Bi

t

Int

e

rna

l

Sa

m

p

li

ng

Fr

eq

./P

e

rio

d

(24 MHz)

Maste

r

Baud Ra

te

(nom

inal)

St

a

rt

/S

to

p

Ho

ld

T

ime

(8 cl

o

c

ks)

00b

Standard

/16

16

1.5 MHz/667 ns

93.75 kHz

5.3

s

01b

Fast

/4

16

6 MHz/167 ns

375 kHz

1.33

s

10b

Standard

/16

32

1.5 MHz/667 ns

46.8 kHz

10.7

s

11b

Reserved

Table 28-4. Enable Master/Slave Block Operation

Enable

Master

Enable

Slave

Block Operation

No

No

Disabled:

The block is disconnected from the GPIO pins, P1[5]

and P1[7]. (The pins may be used as general purpose

I/O.) When either the master or slave is enabled, the

GPIO pins are under control of the I

2

C hardware and

are unavailable.

All internal registers (except I2C_CFG) are held in

reset.

No

Yes

Slave Only Mode:

Any external Start condition will cause the block to

start receiving an address byte. Regardless of the cur-

rent state, any Start resets the interface and initiates a

Receive operation. Any Stop will cause the block to

revert to an idle state

The I2C_MSCR register is held in reset.

Yes

No

Master Only Mode:

External Start conditions are ignored in this mode. No

Byte Complete interrupts on external traffic are gener-

ated, but the Bus Busy status bit continues to capture

Start and Stop status, and thus may be polled by the

master to determine if the bus is available.

Full multi-master capability is enabled, including clock

synchronization and arbitration.

The block will generate a clock based on the setting in

the Clock Rate register

Yes

Yes

Master/Slave Mode:

Both master and slave may be operational in this

mode. The block may be addressed as a slave, but

firmware may also initiate Master mode transfers.

In this configuration, when a master loses arbitration

during an address byte, the hardware will revert to

Slave mode and the received byte will generate a

slave address interrupt.

Содержание CY8C28 series

Страница 65: ...64 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G RAM Paging ...

Страница 85: ...84 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Internal Main Oscillator IMO ...

Страница 93: ...92 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G External Crystal Oscillator ECO ...

Страница 97: ...96 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Phase Locked Loop PLL ...

Страница 125: ...124 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Страница 311: ...310 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G IDAC_CR0 1 FDh ...

Страница 317: ...316 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Страница 393: ...392 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Страница 425: ...424 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Analog Reference ...

Страница 461: ...460 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Two Column Limited Analog System ...

Страница 477: ...476 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Digital Clocks ...

Страница 483: ...482 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Multiply Accumulate MAC ...

Страница 513: ...512 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Internal Voltage Reference ...

Страница 523: ...522 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Switch Mode Pump SMP ...

Страница 533: ...532 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G I O Analog Multiplexer ...

Страница 537: ...536 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Real Time Clock RTC ...

Страница 561: ...560 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...