Emulation Timing Calculations

E-8

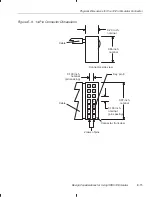

Example E–1. Key Timing for a Single-Processor System Without Buffers

t

pd

ǒ

TCK_RET-TMS

ń

TDI

Ǔ

+

ƪ

t

d

ǒ

TMSmax

Ǔ

)

t

su

ǒ

TTMS

Ǔ

ƫ

t

TCKfactor

+

(20 ns

)

10 ns)

0.4

+

75 ns, or 13.3 MHz

t

pd

ǒ

TCK_RET–TDO

Ǔ

+

ƪ

t

d

ǒ

TTDO

Ǔ

)

t

su

ǒ

TDOmin

Ǔ

ƫ

t

TCKfactor

+

(15 ns

)

3 ns)

0.4

+

45 ns, or 22.2 MHz

In this case, because the TCK_RET-to-TMS/TDI path requires more time to

complete, it is the limiting factor.

Example E–2. Key Timing for a Single- or Multiple-Processor System With Buffered Input

and Output

t

pd (TCK_RET-TMS

ń

TDI)

+

ƪ

t

d (TMSmax

)

)

t

su (TTMS

)

)

t

bufskew

ƫ

t

TCKfactor

+

(20 ns

)

10 ns

)

1.35 ns)

0.4

+

78.4 ns, or 12.7 MHz

t

pd (TCK_RET–TDO)

+

ƪ

t

d (TTDO

)

)

t

su (TDOmin)

)

t

d (bufmax

)

ƫ

t

TCKfactor

+

70 ns, or 14.3 MHz

+

(15 ns

)

3 ns

)

10 ns)

0.4

In this case also, because the TCK_RET-to-TMS/TDI path requires more time

to complete, it is the limiting factor.