Emulation Design Considerations

E-19

Design Considerations for Using XDS510 Emulator

Of the following two cases, the worst-case path delay is calculated to deter-

mine the maximum system test clock frequency.

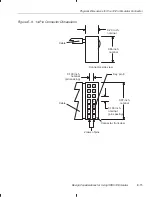

Example E–3. Key Timing for a Single-Processor System Without Buffering (SPL)

t

pd

ǒ

TCK-DTMS

Ǔ

+

ƪ

t

d

ǒ

DTMSmax

Ǔ

)

t

d

ǒ

DTCKHmin

Ǔ

)

t

su

ǒ

TTMS

Ǔ

ƫ

t

TCKfactor

+

(31 ns

)

2 ns

)

10 ns)

0.4

+

107.5 ns, or 9.3 MHz

t

pd

ǒ

TCK-DTDI

Ǔ

+

ƪ

t

d

ǒ

TTDO

Ǔ

)

t

d

ǒ

DTCKLmax

Ǔ

)

t

su

ǒ

DTDLmin

Ǔ

ƫ

t

TCKfactor

+

(15 ns

)

16 ns

)

7 ns)

0.4

+

9.5 ns, or 10.5 MHz

In this case, the TCK-to-DTMS/DTDL path is the limiting factor.

Example E–4. Key Timing for a Single- or Multiprocessor-System With Buffered Input

and Output (SPL)

t

pd (TCK-TDMS)

+

ƪ

t

d (DTMSmax)

)

t

ǒ

DTCKHmin

Ǔ

)

t

su (TTMS)

)

t

(bufskew)

ƫ

t

TCKfactor

+

(31 ns

)

2 ns

)

10 ns

)

1.35 ns)

0.4

+

110.9 ns, or 9.0 MHz

t

pd (TCK–DTDI)

+

ƪ

t

d (TTDO)

)

t

d

ǒ

DTCKLmax

Ǔ

)

t

su (DTDLmin

)

)

t

d (bufskew)

ƫ

t

TCKfactor

+

120 ns, or 8.3 MHz

+

(15 ns

)

15 ns

)

7 ns

)

10 ns)

0.4

In this case, the TCK-to-DTDI path is the limiting factor.