5-7

BRC-300/300P

BRU-300/300P

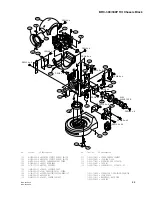

5-6. BRBK-303 (MX-107 Board) Circuit

Description

The BRBK-303 is installed in BRC-300/300P for optical

communication with BRU-300/300P.

Data Transmission

The data sent from BRC-300/300P is classified into two

groups, and then multiplexed by IC9005 to IC9008 into

16-bit data.

.

Group 1

8-bit Y data

KEY (character data)

KEY BLK data (character’s background)

TX (serial control data)

Remaining 4-bit: GND

.

Group 2

8-bit CbCr data

H REF

C SYNC/V SYNC/H SYNC

FLD/VD/HD

6.75MHz clock

The gigabit transceiver converts multiplexed 16-bit data to

serial data with the 54 MHz clock, and then the laser

transceiver unit converts the serial data to an optical signal

and sends it to BRU-300/300P.

Data Reception

The laser transceiver unit converts the optical signal sent

from BRU-300/300P to electrical signal, and then the

gigabit transceiver separates it into the following signals

and sends them to BRC-300/300P.

INT/EXT

VD

RX (serial control data)

TEST signal

The gigabit transceiver restores 54 MHz clock from the

signals received, and then IC9002 divides the 54 MHz

clock into 27 MHz clock and sends it to BRC-300/300P as

a reference signal from BRU-300/300P.

Power Supply Circuit

DC voltages

+

12 V and CPU

+

3.3 V are supplied from

BRC-300/300P. Further, the DC-DC converter generates

+

3.3 V DC and

+

2.5 V DC from the

+

12 V.

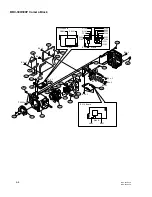

5-7. BRBK-304 (DV-33 Board) Circuit

Description

BRBK-304 converts the video signals sent from BRC-300/

300P or BRU-300/300P to DV format, and then outputs

the video signal on the i.LINK (IEEE1394) interface to

external device.

Video/Audio Signal Processing

The 8-bit video data Y and CbCr sent from BRC-300/300P

or BRU-300/300P are multiplexed by IC008, and are

converted to SMPTE125M-compliant video signal. SAV

(Start of Active Video) and EAV (End of Active Video)

codes are added to the video signal based on the FLD, VD

and HD signals. Then the video signal is output to the sync

detector IC401 (1/2).

In the sync detector IC401 (1/2), the FLD, VD and HD

signals are detected from SAV and EAV in the video

signal sent from IC008, and are then output to the DV

compressor IC206 together with the video signal.

The DV compressor IC206 compresses the signals from

IC401 (1/2) in a DV format, and then outputs them to the

i.LINK packet generator IC401 (2/2).

In the audio interleave IC301, the interleave processing in

a DV format of the mute signal is performed. Then the

audio data is output to the i.LINK packet generator IC401

(2/2).

The i.LINK packet generator IC401 (2/2) generates the

i.LINK isochronous packets (a 480-byte unit) from the

video/audio data sent from the DV compressor IC206 and

audio interleave IC301. At this time, additional informa-

tion data is input from the SP CPU IC603. The i.LINK

isochronous packets are output to the DV OUT connector

CN501 through the IEEE1394 controller IC506.

Synchronization and Clock

The timing generator IC303 generates sync signals (FLAT

and FLTT) and clock synchronizing with the frame signal

(SEL_FD) from IC206.

The video/audio data output from IC206 and IC301 are

communicated to the i.LINK packet generator IC401 (2/2)

in synchronization with these timing signals.