5-1

BRC-300/300P

BRU-300/300P

Section 5

Circuit Description

5-1. BRC-300/300P Circuit Description

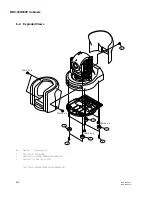

5-1-1. Camera Block

Lens Block

In the lens block, the video image that is input from the

lens is received by the three CCDs through the R/G/B

filters after dispersion to the RGB in the prism. Each color

video signal stored in each CCD is extracted by each CDS

circuit for R/G/B.

CDS: Correlated Double Sampling

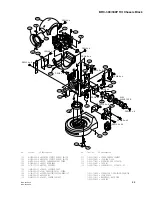

VC-343 Board

The timing generator IC503 drives the CCD at 66 MHz

(for NTSC system) or at 54 MHz (for PAL system).

R/G/B video signals from the CDS circuits are converted

to each 14-bit digital signal by the A/D converters IC504,

IC505 and IC506, and then gamma-corrected and aperture

processed by the camera signal DSP IC602.

The pixel converter IC701 converts 1070000-pixel signal

to 720

x

480 pixels (NTSC) or 720

x

576 pixels (PAL)

signal.

A signal from the pixel converter IC701 is converted to 8-

bit Y signal and 8-bit C (Cb/Cr multiplexed) signal, and

then transferred to the IF-944 board.

The camera microcomputer IC902 controls the lens and the

camera circuit.

The EEPROM IC901 saves adjustment data and mode data

of the camera drive system, which must be retained even

during power OFF.

DSP: Digital Signal Processor

IF-110 Board

The VISCA microcomputer IC403 sends/receives control

signals and status signals to/from the microcomputer on

the SY-314 board with the VISCA protocol.

The EEPROM IC404 saves VISCA microcomputer data

that must be retained even during power OFF.

Motors for zooming, focusing and iris are controlled by the

camera microcomputer on the VC-343 board. The control-

ler IC304 and the driver IC303 control these motors.

VISCA: Video System Control Architecture

DD-208 Board

The DC-DC converter DD001 generates power voltages

required in the camera block from the external 12 V DC

supplied through the SY-314, CC-91 and IF-944 boards.

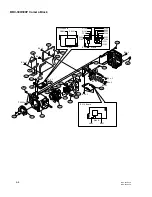

5-1-2. IF-944 Board

The IF-944 board converts 8-bit Y and C data, sync pulses

(HD/VD/FLD) and 13.5 MHz clock from the camera block

to four LVDS serial signals, and then sends the signals to

the CC-91 board.

It also relays

+

12 V power and serial data to the camera

block. The board is equipped with a tally display LED

driver and

+

3.3 V/

+

5 V series regulators.

IC2003 generates 27 MHz clock locked to the 13.5 MHz

clock from the camera block. The LVDS transmitter

IC2002 generates 189 MHz (27

x

7) clock from the 27

MHz clock, and converts camera signals to 3-channel

LVDS data and 1-channel LVDS clock using the generated

clock.

The

+

3.3 V and

+

5 V necessary for the IF-944 board

circuit are regulated from

+

12 V by the series regulators.

LVDS: Low Voltage Differential Signal