APPLICATIONS

7751 Group User’s Manual

17–17

17.1 Memory expansion

Memory

EPROM

One-time PROM

Flash memory

SRAM

_

➂

When using external memory that outputs data for more than t

pzx(E-P1Z/P2Z)

after rising of E

signal

_

Because the external memory outputs data for more than t

pzx(E-P1Z/P2Z)

after rising of the E signal,

there will be a possibility of the tail of data colliding with the head of address. In such a case,

examine the method described below:

●

Cut the tail of data output from the external memory by using, for example, a bus buffer.

●

Use the Mitsubishi’s memory chips that can be connected without a bus buffer.

Figures 17.1.13 to 17.1.20 show examples for how to use a bus buffer and the timing charts. Table

17.1.5 lists the memory chips that can be connected a without bus buffer. When using one of these

memory chips, the user can connect it to the user’s microcomputer without a bus buffer because

timing parameters t

DF

and t

dis(OE)

listed below are guaranteed. (However, the read signal must go

_

high within 10 ns after rising of E signal.)

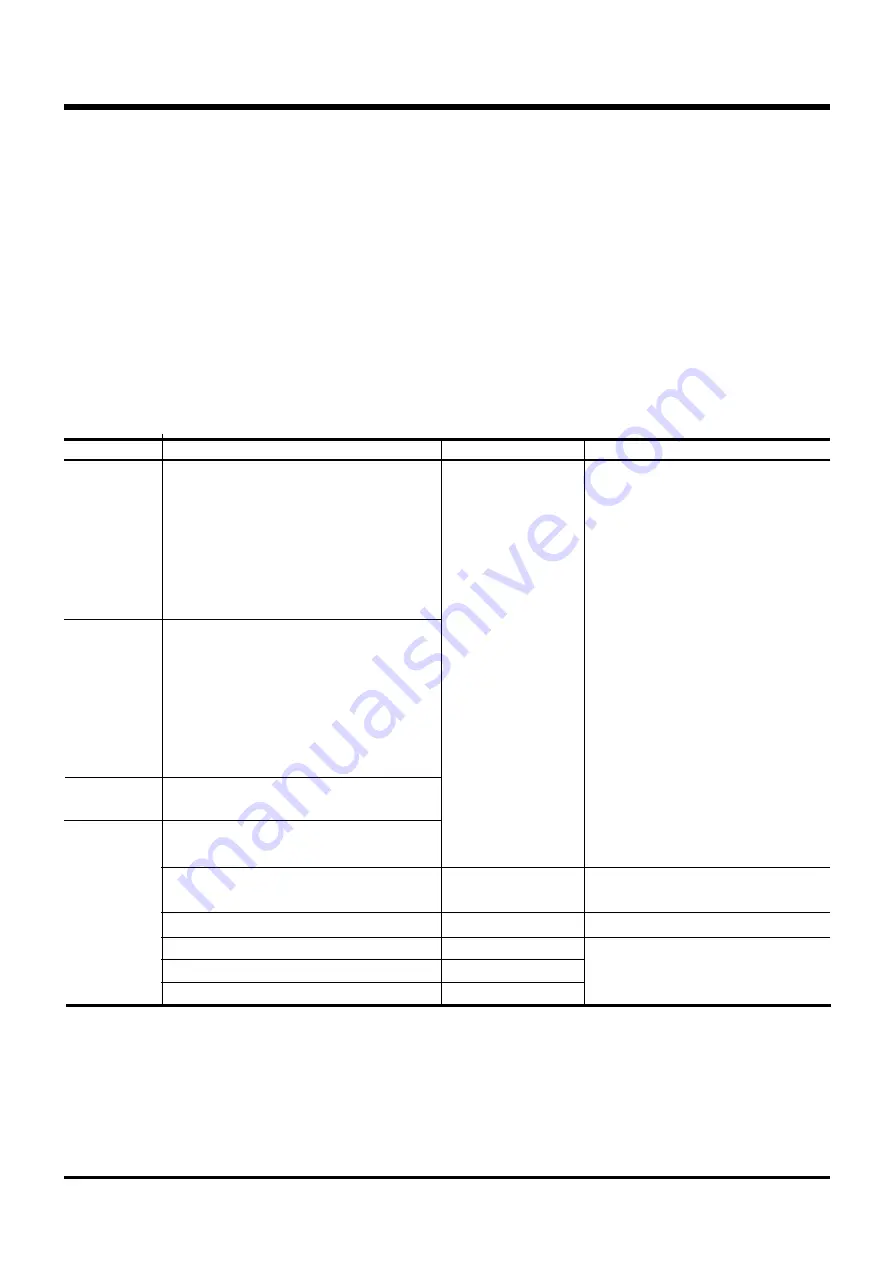

Table 17.1.5 Memory chips that can be connected without bus buffer

t

DF

/t

dis(OE)

(Maximum)

15 ns

(when guaranteeing by

kit) (Note)

8 ns

10 ns

6 ns

7 ns

8 ns

Conditions

f(X

IN

)

≤

20 MHz, at low–speed running

f(X

IN

)

≤

40 MHz, at high–speed running

f(X

IN

)

≤

25 MHz, at low–speed running

f(X

IN

)

≤

25 MHz, at low–speed running

f(X

IN

)

≤

40 MHz, at high–speed running

f(X

IN

)

≤

25 MHz, at low–speed running

Type description

M5M27C256AK-85, -10, -12, -15

M5M27C512AK-10, -12, -15

M5M27C100K-12. -15

M5M27C101K-12, -15

M5M27C102K-12, -15

M5M27C201K, JK-10, -12, -15

M5M27C202K, JK-10, -12, -15

M5M27C256AP, FP, VP, RV-12, -15

M5M27C512AP, FP-15

M5M27C100P-15

M5M27C101P, FP, J, VP, RV-15

M5M27C102P, FP, J, VP, RV-15

M5M27C201P, FP, J, VP, RV-12, -15

M5M27C202P, FP, J, VP, RV-12, -15

M5M28F101P, FP, J, VP, RV-10, -12, -15

M5M28F102FP, J, VP, RV-10, -12, -15

M5M5256CP, FP, KP, VP, RV-55LL, -55XL,

-70LL, -70XL, -85LL, -85XL, -10LL, -10XL

M5M5278CP, FP, J-20, -20L

M5M5278CP, FP, J-25, -25L

M5M5278DP, J-12

M5M5278DP, FP, J-15, -15L

M5M5278DP, FP, J-20, -20L

Note: When the user want specifications of the memory chips listed above, add a comment “t

DF

/t

dis(OE)

15 ns

product, microcomputer and kit.”

Summary of Contents for 7700 FAMILY

Page 2: ...MITSUBISHI 16 BIT SINGLE CHIP MICROCOMPUTER 7700 FAMILY 7751 SERIES 7751 Group User s Manual...

Page 11: ...Table of Contents viii 7751 Group User s Manual MEMORANDUM...

Page 157: ...TIMER B 6 28 7751 Group User s Manual 6 5 Pulse period pulse width measurement mode MEMORANDUM...

Page 245: ...7751 Group User s Manual 8 36 A D CONVERTER Precautions when using A D converter MEMORANDUM...

Page 265: ...7751 Group User s Manual WAIT MODE 11 6 11 3 Precautions for Wait mode MEMORANDUM...

Page 289: ...CONNECTION WITH EXTERNAL DEVICES 12 4 Hold function 7751 Group User s Manual 12 24 MEMORANDUM...

Page 290: ...CHAPTER 13 RESET 13 1 Hardware reset 13 2 Software reset...

Page 302: ...CHAPTER 14 CLOCK GENERATING CIRCUIT 14 1 Oscillation circuit example 14 2 Clock...

Page 307: ...CLOCK GENERATING CIRCUIT 7751 Group User s Manual 14 6 14 2 Clock MEMORANDUM...

Page 360: ...CHAPTER 16 STANDARD CHARACTERISTICS 16 1 Standard characteristics...

Page 366: ...CHAPTER 17 APPLICATIONS 17 1 Memory expansion...

Page 405: ...APPLICATIONS 7751 Group User s Manual 17 40 17 1 Memory expansion MEMORANDUM...

Page 406: ...CHAPTER 18 PROM VERSION 18 1 EPROM mode 18 2 Usage precaution...

Page 417: ...7751 Group User s Manual PROM VERSION 18 12 18 2 Usage precaution MEMORANDUM...

Page 418: ...CHAPTER 19 FLASH MEMORY VERSION 19 1 Parallel input output mode 19 2 Serial input output mode...

Page 451: ...FLASH MEMORY VERSION 7751 Group User s Manual 19 34 19 2 Serial input output mode MEMORANDUM...

Page 484: ...APPENDIX 7751 Group User s Manual 20 33 Appendix 4 Package outlines 80D0...

Page 489: ...APPENDIX 7751 Group User s Manual 20 38 Appendix 6 Hexadecimal instruction code table...

Page 490: ...APPENDIX 7751 Group User s Manual 20 39 Appendix 6 Hexadecimal instruction code table...

Page 492: ...APPENDIX 7751 Group User s Manual 20 41 Appendix 7 Machine instructions...

Page 493: ...APPENDIX 7751 Group User s Manual 20 42 Appendix 7 Machine instructions...

Page 494: ...APPENDIX 7751 Group User s Manual 20 43 Appendix 7 Machine instructions...

Page 495: ...APPENDIX 7751 Group User s Manual 20 44 Appendix 7 Machine instructions...

Page 496: ...APPENDIX 7751 Group User s Manual 20 45 Appendix 7 Machine instructions...

Page 497: ...APPENDIX 7751 Group User s Manual 20 46 Appendix 7 Machine instructions...

Page 498: ...APPENDIX 7751 Group User s Manual 20 47 Appendix 7 Machine instructions...

Page 499: ...APPENDIX 7751 Group User s Manual 20 48 Appendix 7 Machine instructions...

Page 500: ...APPENDIX 7751 Group User s Manual 20 49 Appendix 7 Machine instructions...

Page 501: ...APPENDIX 7751 Group User s Manual 20 50 Appendix 7 Machine instructions...

Page 502: ...APPENDIX 7751 Group User s Manual 20 51 Appendix 7 Machine instructions...

Page 503: ...APPENDIX 7751 Group User s Manual 20 52 Appendix 7 Machine instructions...

Page 504: ...APPENDIX 7751 Group User s Manual 20 53 Appendix 7 Machine instructions...

Page 505: ...APPENDIX 7751 Group User s Manual 20 54 Appendix 7 Machine instructions...

Page 506: ...APPENDIX 7751 Group User s Manual 20 55 Appendix 7 Machine instructions...

Page 507: ...APPENDIX 7751 Group User s Manual 20 56 Appendix 7 Machine instructions...

Page 508: ...APPENDIX 7751 Group User s Manual 20 57 Appendix 7 Machine instructions...

Page 509: ...APPENDIX 7751 Group User s Manual 20 58 Appendix 7 Machine instructions...

Page 510: ...APPENDIX 7751 Group User s Manual 20 59 Appendix 7 Machine instructions...

Page 511: ...APPENDIX 7751 Group User s Manual 20 60 Appendix 7 Machine instructions...

Page 535: ...APPENDIX Appendix 9 Q A 7751 Group User s Manual 20 84 MEMORANDUM...

Page 536: ...GLOSSARY...

Page 539: ...GLOSSARY 7751 Group User s Manual 4 MEMORANDUM...