529

Chapter 11

16-bit Timer/Event Counter T

User’s Manual U16580EE3V1UD00

(c) Rewrite timing of bit TTnECC

When TTnCE = 0 and TTnECC = 0, setting TTnCE = 1 causes the setting value of the TTnTCW

register to be loaded to the counter. Perform rewrite of the TTnECC bit after the operation clock

has become valid (after several clocks: TBD), following setting of TTnCE = 1.

If bit TTnECC is rewritten before the operation clock becomes valid, counting starts from FFFFH

without loading the setting value of the TTnTCW register to the counter.

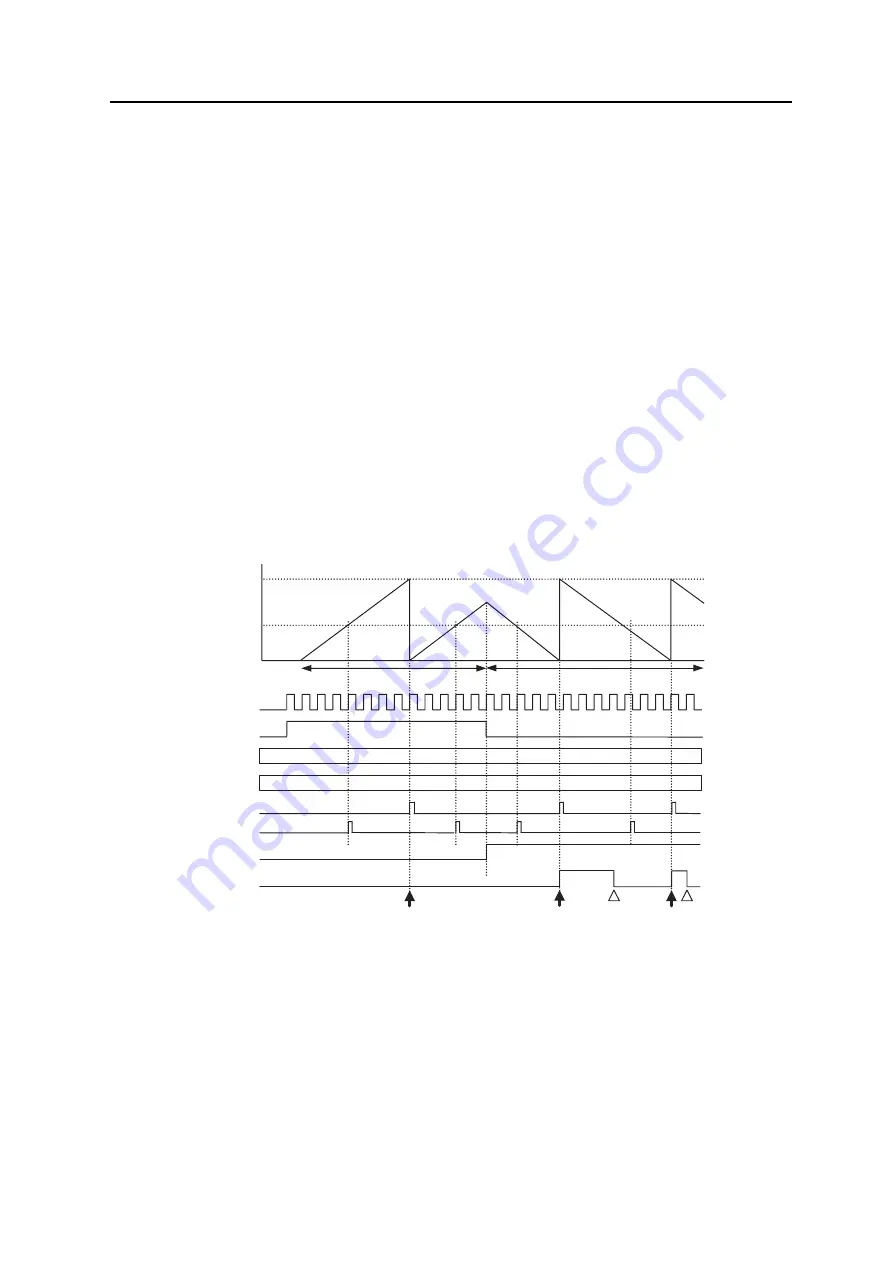

Figure 11-37:

Counter Hold through Bit TTnECC Timings (3/5)

(e) Basic Timing in Encoder Compare Mode (1)

< Register setting conditions>

•

TTnCTL0: TTnMD3 to 0 = 1000B

Encoder compare mode

•

TTnCTL1: TTnUDS1, 0 = 00B

Judgment of up/down count with count judgment mode 1

•

TTnCTL1: TTnECM1, 0 = 01B

Counter clear upon match between counter value and

TTnCCR0 buffer register

•

TTnCTL1: TTnLDE = 1

Loading of setting value of TTnCCR0 register (p) upon

underflow occurrence

•

TTnIOC3: TTnEIS1, 0 = 01B

Detection of rising edge of TENCTn0 and TENCTn1 pin

inputs

•

TTnIOC3: TTnSCE = 0,

TTnECS1-0 = 00B

Valid edge detection clear (no edge specified)

Since TTnUDS1, 0 and TTnEIS1, 0 that control the count operation are set to 00B and 01B

(rising edge detection), respectively, the counter is operated through detection of the phase of pin

TENCTn1 upon detection of the rising edge of TENCTn0 pin input. A compare match interrupt

(INTTTnCC0) is output upon a match between the counter value and the TTnCCR0 compare reg-

ister (p). At this time, the counter is cleared to 0000H if the next count operation is up count.

A compare match interrupt (INTTTnCC1) is output upon a match between the counter value and

the TTnCCR1 buffer register (q). The counter is not cleared upon a match between the counter

value and the TTnCCR1 register. If underflow occurs when TTnLDE = 1 is set, the setting value of

the TTnCCR0 buffer register (m) is loaded to the counter. A count operation is possible between

0000H and the setting value of the TTnCCR0 register by setting TTnLDE = 1 and TTnECM0 = 1.

Remark:

n = 0, 1

p

TTnCCR0

p

TTnESF

TTnEUF

q

TTnCCR1

q

INTTTnCC0

INTTTnCC1

TENCTn0

TENCTn1

Encoder

counter

Count clear

Load to counter

Load to counter

Up count

Down count

Summary of Contents for MuPD70F3187

Page 6: ...6 Preface User s Manual U16580EE3V1UD00 ...

Page 16: ...16 User s Manual U16580EE3V1UD00 ...

Page 28: ...28 User s Manual U16580EE3V1UD00 ...

Page 32: ...32 User s Manual U16580EE3V1UD00 ...

Page 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO ...

Page 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO ...

Page 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO ...

Page 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00 ...

Page 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO ...

Page 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 ...

Page 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO ...

Page 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO ...

Page 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO ...

Page 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO ...

Page 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO ...

Page 1052: ...1052 User s Manual U16580EE3V1UD00 ...

Page 1053: ......