186

User’s Manual U11302EJ4V0UM

CHAPTER 11 BUZZER OUTPUT CONTROLLER

11.1 Buzzer Output Controller Functions

The buzzer output controller outputs a 1.2 kHz, 2.4 kHz, or 4.9 kHz frequency square-wave. The buzzer

frequency selected by timer clock select register 2 (TCL2) is output from the BUZ/P36 pin.

Follow the procedure below to output the buzzer frequency.

[1] Select the buzzer output frequency using bits 5 to 7 (TCL25 to TCL27) of TCL2.

[2] Set the P36 output latch to 0.

[3] Set bit 6 (PM36) of port mode register 3 (PM3) to 0 (set to output mode).

Caution

Buzzer output cannot be used when the P36 output latch is set to 1.

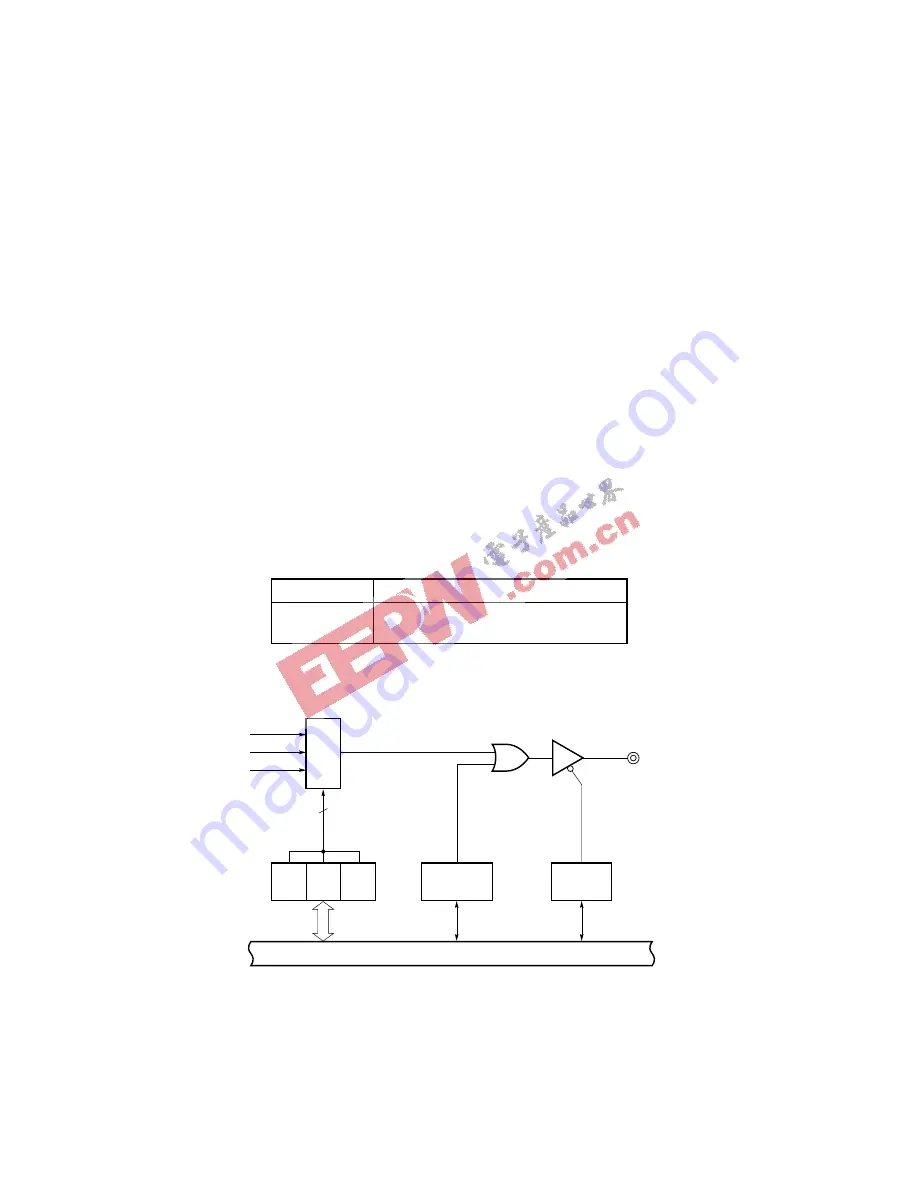

11.2 Buzzer Output Controller Configuration

The buzzer output controller consists of the following hardware.

Table 11-1. Buzzer Output Controller Configuration

Item

Configuration

Control registers

Timer clock select register 2 (TCL2)

Port mode register 3 (PM3)

Figure 11-1. Buzzer Output Controller Block Diagram

f

X

/2

10

f

X

/2

11

f

X

/2

12

P36

output

latch

3

BUZ/P36

PM36

TCL27TCL26TCL25

Internal bus

Timer clock select

register 2

Port mode register 3

Selector