+V3_3

+VSBY5_0

+VSBY5_0;14

GND;7

+VSBY5_0;14

GND;7

+VSBY5_0;14

GND;7

+VSBY5_0

+VSBY5_0

+VSBY3_3

+V3_3

+V3_3

+V5_0

INTEL(R) E7500 CHIPSET CUSTOMER REFERENCE SCHEMATICS

R

D

C

B

B

D

C

1

1

2

3

4

5

6

7

8

2

3

4

5

6

7

8

A

A

LAST REVISED:

1900 Prairie City Road

Folsom, California 095630

TITLE:

Platform Apps Engineering

SHEET

03/04/02

+VSBY3_3

+VSBY5_0

+VSBY3_3

+VSBY5_0

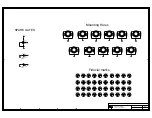

Pull-ups for fan tach on fan cntl board

Install jumpers to short pin pairs

5 and 6, 7 and 8, 9 and 10, 17 and 18,

19 and 20, 29 and 30

FRONT PANEL CONNECTOR

For Test Purposes Only

80

1

10

11

12

13

14

15

16

17

18

19

2

20

21

22

23

24

25

26

27

28

29

3

30

4

5

6

7

8

9

J43

ICH3_SMI_N

53

0.

1U

F

C

1514

C

1513

0.

1U

F

0.

1U

F

C

1516

C

1517

0.

1U

F

0.

1U

F

C

1518

C

1519

0.

1U

F

0.

1U

F

C

1520

C

1521

0.

1U

F

0.

1U

F

C

1522

C

1515

0.

1U

F

30

28

26

24

22

20

18

16

14

12

10

8

6

4

2

29

27

25

23

21

19

17

15

13

11

9

7

5

3

1

J71

CONN_PS_ON_N

60

4,6

CPU_PROC_HOT_N

CPU1_SKTOCC_N

4,7

CPU0_SKTOCC_N

6

PS_ON_N

60

CPU0_SMI_N

6,9

CPU1_SMI_N

4,9

SYS_SLP_S5_N

60,81

ICH3_SLP_S5_N

55

CPU_LINT1_NMI

4,6,9

ICH3_LINT1_NMI

53

P64H2_2_RASERR_N

33

PS_PWRGD

60

PS_PWRGD_SYS

60,64

P64H2_1_RASERR_N

29

I2C_BUS3_DAT

16-19,22-25,65,81

I2C_BUS3_CLK

16-19,22-25,65,81

R

792

10K

NO

P

O

P

I2C_BUS0_DAT

60,80,81

60,80,81

I2C_BUS0_CLK

FAN_TACH[7:0]

FAN_TACH3

FAN_TACH7

FAN_TACH6

FAN_TACH5

FAN_TACH4

FAN_TACH0

FAN_TACH1

FAN_TACH2

FAN_TACH7

FAN_TACH6

FAN_TACH5

FAN_TACH4

FAN_TACH3

FAN_TACH2

FAN_TACH1

FAN_TACH0

55

ICH3_PWRBTN_N

PWROK_RST_N

64

R

910

1K

1K

R

909

R

790

10K

10K

R

793

R

794

10K

C

1534

NOPOP 56P

F

4

3

U113

1

2

U113

C

1532

NOPOP 56P

F

56P

F

NOPOP

C

1533

5

6

U113

R

908

1K

FP_COOL_FLT_LED

FP_SYS_FLT_LED

FP_PWR_LED

ICH3_INTRUDER_N

54

FP_HD_ACT_N

56

FP_NMI_BTN_N

FP_SLP_BTN_N

1

2

3

4

5

6

7

8

R

P

288

4.

7K

8

7

6

54

3

2

1

4.

7K

R

P

289

I2C_BUS2_CLK

4,6,11,81

I2C_BUS1_CLK

29,33,42,44,45,81

I2C_BUS0_CLK

60,80,81

I2C_BUS2_DAT

4,6,11,81

I2C_BUS1_DAT

29,33,42,44,45,81

I2C_BUS0_DAT

60,80,81

Summary of Contents for Xeon

Page 24: ...Introduction 24 Design Guide This page is intentionally left blank ...

Page 30: ...Component Quadrant Layout 30 Design Guide This page is intentionally left blank ...

Page 52: ...Platform Clock Routing Guidelines 52 Design Guide This page is intentionally left blank ...

Page 66: ...System Bus Routing Guidelines 66 Design Guide This page is intentionally left blank ...

Page 118: ...Intel 82870P2 P64H2 118 Design Guide This page is intentionally left blank ...

Page 146: ...I O Controller Hub 146 Design Guide This page is intentionally left blank ...

Page 148: ...Debug Port 148 Design Guide This page is intentionally left blank ...

Page 210: ...Schematic Checklist 210 Design Guide This page is intentionally left blank ...

Page 220: ...Layout Checklist 220 Design Guide This page is intentionally left blank ...

Page 222: ...Schematics 222 Design Guide This page is intentionally left blank ...