IDE Configuration

12-6

Intel® 460GX Chipset Software Developer’s Manual

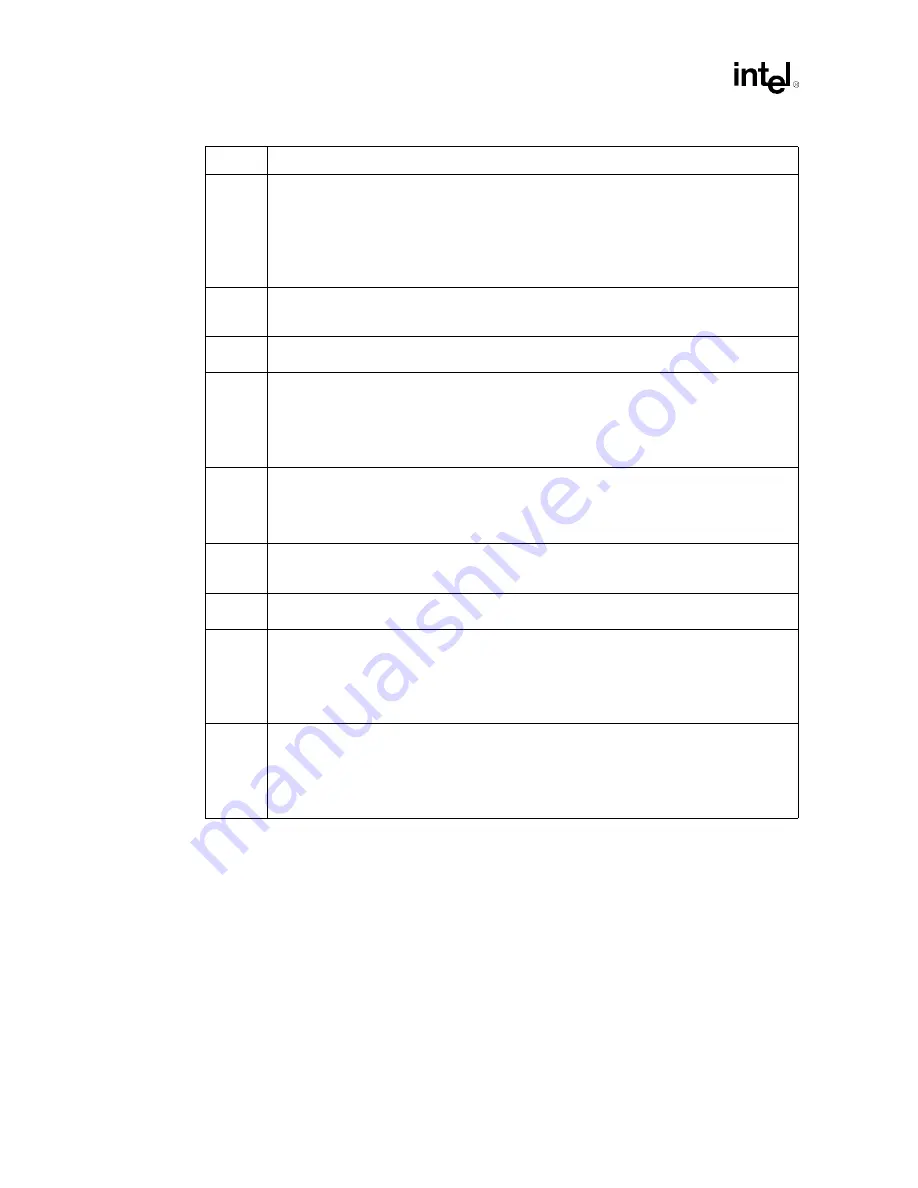

12.2.11

SIDETIM–Slave IDE Timing Register (Function 1)

Address Offset:

44h

Default Value:

00h

Attribute:

Read/Write only

This register controls the IFB’s IDE interface and selects the timing characteristics for the slave

drives on each IDE channel. This allows for programming of independent operating modes for

each IDE agent. This register has no affect unless the SITRE bit is enabled in the IDETIM Register.

9:8

Recovery Time (RTC). This field selects the minimum number of PCI clocks between the last

IORDY# sample point and the DIOx# strobe of the next cycle.

Bits[9:8] Number of Clocks

00 4

01 3

10 2

11 1

7

DMA Timing Enable Only (DTE1). When DTE1=1, fast timing mode is enabled for DMA data

transfers for drive 1. PIO transfers to the IDE data port will run in compatible timing. When DTE1 =

0, both DMA and PIO data transfers for drive 1 will use the fast timing mode.

6

Prefetch and Posting Enable (PPE1). When PPE1=1, prefetch and posting to the IDE data port

is enabled for drive 1. When PPE1 = 0, prefetch and posting is disabled for drive 1.

5

IORDY Sample Point Enable Drive Select 1 (IE1). When IE1=0, IORDY sampling is disabled for

Drive 1. When the internal IORDY signal is forced asserted, IORDY is sampled asserted at the first

sample point as specified by the ISP field in this register.

When IE1=1 and the currently selected drive (via a copy of bit 4 of 1x6h) is Drive 1, all accesses to

the enabled I/O address range sample IORDY. The IORDY sample point is specified by the ISP

field in this register.

4

Fast Timing Bank Drive Select 1 (TIME1). When cleared, accesses to the data port will use

compatible timings for this drive. When set and bit 14 cleared, accesses to the data port will use

bits 13:12 for the IORDY sample point, and bits 9:8 for the recovery time. When set and bit 14 set,

accesses to the data port will use the IORDY sample point and recover time specified in the slave

IDE timing register.

3

DMA Timing Enable Only (DTE0). When DTE0=1, fast timing mode is enabled for DMA data

transfers for drive 0. PIO transfers to the IDE data port will run in compatible timing. When DTE1 =

0, both DMA and PIO data transfers for drive 0 will use the fast timing mode.

2

Prefetch and Posting Enable (PPE0). When PPE0 = 1, prefetch and posting to the IDE data port

is enabled for drive 0. When PPE0 = 0, prefetch and posting is disabled for drive 0.

1

IORDY Sample Point Enable Drive Select 0 (IE0). When IE0=0, IORDY sampling is disabled for

Drive 0. When the internal IORDY signal is forced asserted, IORDY is sampled asserted at the first

sample point as specified by the ISP field in this register.

When IE0=1 and the currently selected drive (via a copy of bit 4 of 1x6h) is Drive 0, all accesses to

the enabled I/O address range sample IORDY. The IORDY sample point is specified by the ISP

field in this register.

0

Fast Timing Bank Drive Select 0 (TIME0). When TIME0=0, accesses to the data port of the

enabled I/O address range uses the 16 bit compatible timing.

When TIME0=1 and the currently selected drive (via a copy of bit 4 of 1x6h) is Drive 0, accesses to

the data port of the enabled I/O address range use fast timings. PIO accesses to the data port use

fast timing only if bit 3 of this register (DTE0) is 0. Accesses to all non-data ports of the enabled I/

O address range always use the 8 bit compatible timings.

Bit

Description

Summary of Contents for 460GX

Page 1: ...Intel 460GX Chipset System Software Developer s Manual June 2001 Document Number 248704 001 ...

Page 20: ...Introduction 1 8 Intel 460GX Chipset Software Developer s Manual ...

Page 80: ...System Architecture 3 8 Intel 460GX Chipset Software Developer s Manual ...

Page 90: ...System Address Map 4 10 Intel 460GX Chipset Software Developer s Manual ...

Page 98: ...Memory Subsystem 5 8 Intel 460GX Chipset Software Developer s Manual ...

Page 146: ...AGP Subsystem 7 16 Intel 460GX Chipset Software Developer s Manual ...

Page 170: ...IFB Register Mapping 9 6 Intel 460GX Chipset Software Developer s Manual ...

Page 190: ...IFB Usage Considerations 10 20 Intel 460GX Chipset Software Developer s Manual ...

Page 232: ...LPC FWH Interface Configuration 11 42 Intel 460GX Chipset Software Developer s Manual ...

Page 244: ...IDE Configuration 12 12 Intel 460GX Chipset Software Developer s Manual ...

Page 258: ...Universal Serial Bus USB Configuration 13 14 Intel 460GX Chipset Software Developer s Manual ...

Page 270: ...SM Bus Controller Configuration 14 12 Intel 460GX Chipset Software Developer s Manual ...

Page 288: ...PCI LPC Bridge Description 15 18 Intel 460GX Chipset Software Developer s Manual ...

Page 294: ...IFB Power Management 16 6 Intel 460GX Chipset Software Developer s Manual ...