Epson Research and Development

Page 33

Vancouver Design Center

Hardware Functional Specification

S1D13704

Issue Date: 01/02/08

X26A-A-001-04

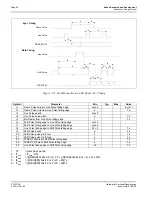

7.1.6 Generic #2 Interface Timing

Figure 7-6: Generic #2 Timing

Note

BCLK may be turned off (held low) between accesses - see Section 13.5, “Turning Off

BCLK Between Accesses” on page 86

Table 7-6: Generic #2 Timing

Symbol

Parameter

Min

Max

Units

f

BCLK

Bus Clock frequency

0

50

MHz

T

BCLK

Bus Clock period

1/f

BCLK

t1

A[15:0], BHE#, CS# valid to WE#, RD# low

0

ns

t2

WE#, RD# high to A[15:0], BHE#,

CS# invalid

0

ns

t3

WE# low to D[15:0] valid (write cycle)

T

BCLK

t4

WE# high to D[15:0] invalid (write cycle)

0

ns

t5

RD# low to D[15:0] driven (read cycle)

16

ns

t6

D[15:0] valid to WAIT# high (read cycle)

0

ns

t7

RD# high to D[15:0] high impedance (read cycle)

10

ns

t8

WE#, RD# low to WAIT# driven low

14

ns

t9

BCLK to WAIT# high

16

ns

t10

WE#, RD# high to WAIT# high impedance

11

ns

t8

t4

t9

t3

t1

t10

BCLK

A[15:0]

CS#

WE#,RD#

WAIT#

VALID

t2

Hi-Z

Hi-Z

Hi-Z

VALID

T

BCLK

t6

t7

VALID

Hi-Z

Hi-Z

D[15:0]

D[15:0]

t5

BHE#

(write)

(read)

*