XMC-6VLX

USER’S MANUAL

Acromag, Inc. Tel: 248-295-0310

- 28 - http://www.acromag.com

- 28 -

www.acromag.com

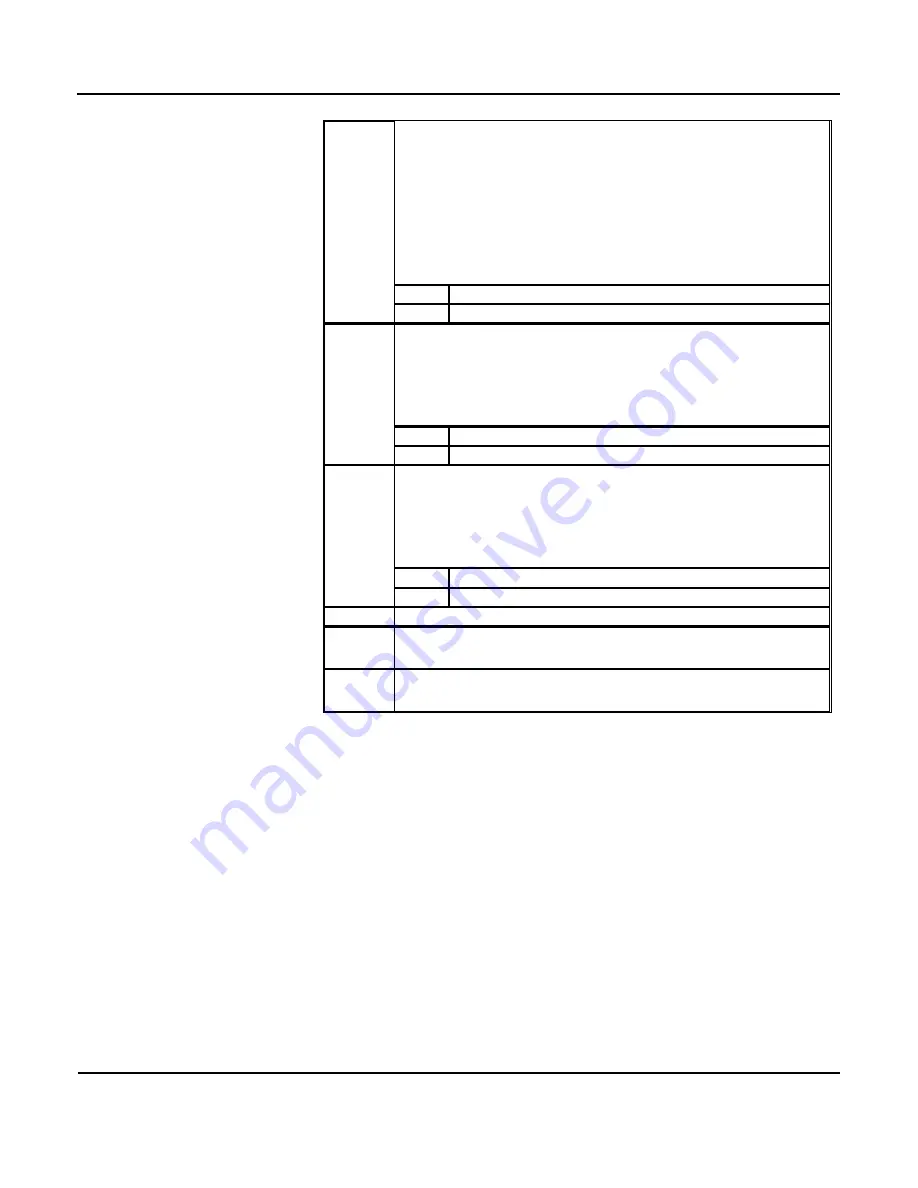

12

Interrupt on Complete. When set to 1, this bit indicates an

interrupt event has been generated on completion of a DMA

transfer (either a Simple or Scatter Gather). If the Interrupt

on Complete (bit-12) of the CDMA Control register = ‘1’, an

interrupt is generated from the AXI CDMA. A CPU write of 1

clears this bit to 0.

Note:

When operating in Scatter Gather mode, the criteria

specified by the interrupt threshold must also be met.

0

No IOC Interrupt

1

IOC Interrupt active

13

Interrupt on Delay. When set to 1, this bit indicates an

interrupt event has been generated on a delay timer time out.

If the Interrupt on Delay Timer bit-13 of the CDMA Control

register = ‘1’, an interrupt is generated from the AXI CDMA. A

CPU write of 1 clears this bit to 0.

0

No Delay Interrupt

1

Delay Interrupt Active

14

Interrupt on Error. When set to 1, this bit indicates an

interrupt event has been generated due to an error condition.

If the Interrupt on Error bit-14 of the CDMA Control register =

‘1’, an interrupt is generated from the AXI CDMA. A CPU write

of 1 clears this bit to 0.

0

No Error Interrupt

1

Error Interrupt Active

15

Reservered

23-16

Interrupt Threshold Status. This field reflects the current

interrupt threshold value in the Scatter Gather Engine.

31-24

Interrupt Delay Time Status. This field reflects the current

interrupt delay timer value in the Scatter Gather Engine.