LH79524/LH79525 User’s Guide

Reset, Clock, and Power Controller

Version 1.0

13-5

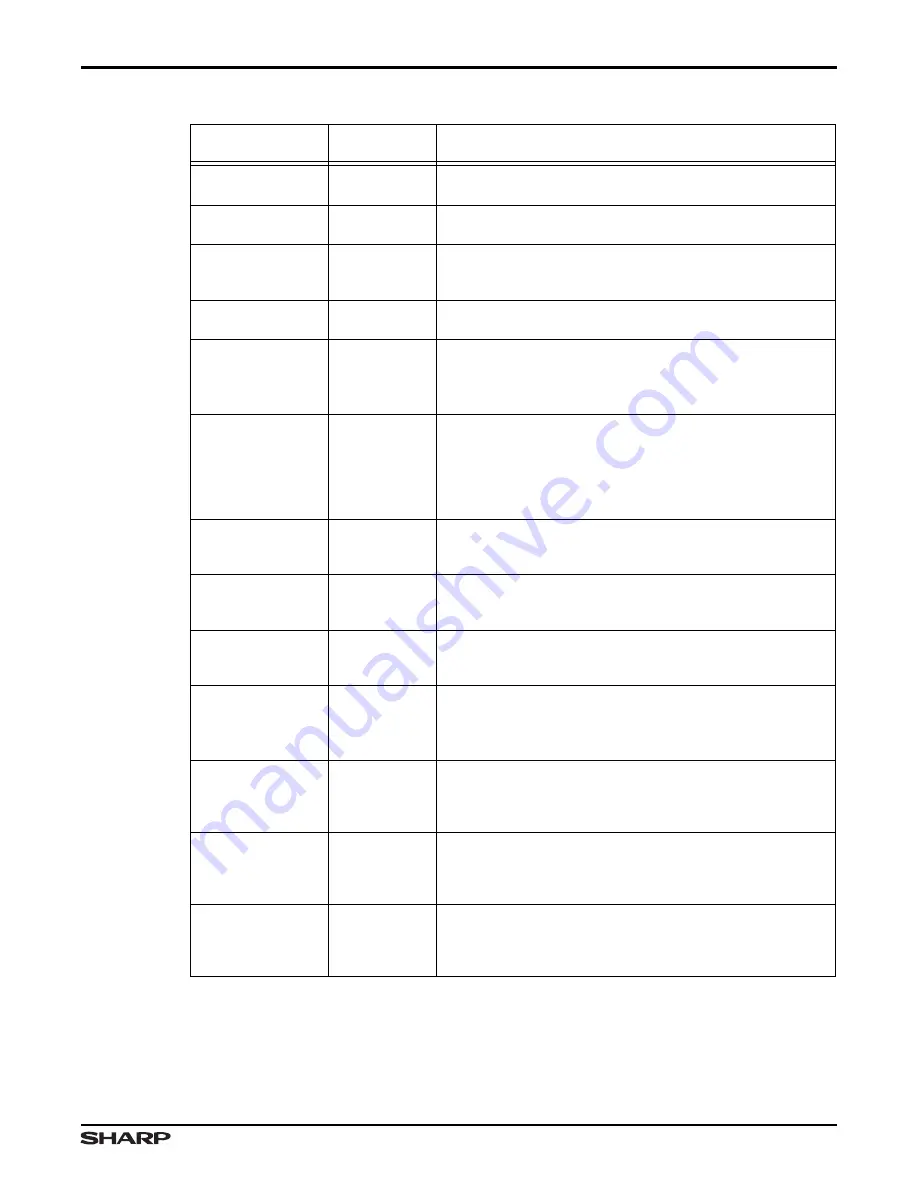

Table 13-1. LH79524/LH79525 Clocks and Maximum Frequencies

NAME

FREQUENCY

(MAX.)

DESCRIPTION

Oscillator Clock

(CLK OSC)

20.0 MHz

External crystal oscillator input; used as the source for the three

UARTs. Also an input to the PLL.

PLL System Clock

(CLK PLL)

304.819 MHz

The PLL System clock originates in the PLL and is input to the

RCPC; asynchronous to all other clocks.

PLL USB Clock

48.0 MHz

Originates in the PLL, can be gated and prescaled in the RCPC.

This input to the USB is required to be 48 MHz; asynchronous to

all other clocks.

32.768 kHz

Oscillator Clock

32.768 kHz

External 32.768 kHz crystal oscillator input.

AHB Clock (HCLK)

50.803 MHz

Originates in the RCPC and is connected to AHB and APB periph-

erals. This clock can be separately prescaled. The clock is halted

HIGH when the RCPC is in any power down mode other than

Standby mode. This clock is synchronous to FCLK_CPU.

AHB Fast CPU Clock

(FCLK CPU)

76.205 MHz

The AHB Fast CPU clock originates in the RCPC and is connect-

ed to the ARM720T core. This clock can be separately prescaled.

The prescaled value can range from CLK_PLL/4 to CLK_PLL/30.

The clock is halted HIGH when the RCPC is in any power down

mode other than Standby. This clock is synchronous to HCLK and

HCLK_CPU.

Ethernet Clock

50.803 MHz

This clock is generated in the RCPC and connected to the Ethernet

block. This clock can be separately enabled/disabled, but is always

the same frequency as HCLK. This clock is synchronous to HCLK.

DMA Clock

50.803 MHz

The DMA clock originates in the RCPC and is connected to the DMA

block. This clock can be separately enabled and disabled, but always

has the same frequency as HCLK. It is synchronous to HCLK.

External Memory

Controller Clock

50.803 MHz

The EMC clock originates in the RCPC and connects to the EMC

block. It can be separately enabled/disabled, but always has the

same frequency as HCLK. This clock is synchronous to HCLK.

SSP Clock

(SSPCLK)

50.803 MHz

The SSP clock originates in the RCPC and is connected to the

SSP block. This clock can be separately enabled, disabled and

prescaled. The prescaled value range is HCLK/1 to HCLK/256.

This clock is asynchronous to all other clocks.

CLCD Clock

(LCDDCLK)

50.803 MHz

The CLCD clock originates in the RCPC and is connected to the

CLCD block. This clock can be separately enabled, disabled and

prescaled. The prescaled value can range from HCLK/1 to HCLK/

256. This clock is asynchronous to all other clocks.

UART[2:0] Clock

20.0 MHz

The UART clocks originate in the RCPC and are connected to the

UART blocks. These are all separate and can be separately en-

abled/disabled. They will always have the same frequency as

CLK_OSC. This clock is asynchronous to all other clocks.

RTC Clock

1.0 Hz

The RTC clock originates in the RCPC and is connected to the RTC

block. This clock can be separately enabled and disabled. It will al-

ways have a frequency of 1 Hz. This clock is asynchronous to all

other clocks.