596

Chapter 14

A/D Converter

User’s Manual U16580EE3V1UD00

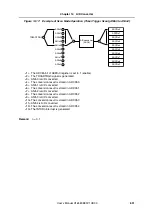

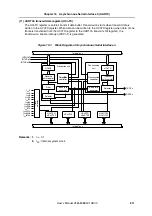

14.6 Operation in Timer Trigger Mode

In this mode, the conversion timing of the analog input signal set by the ANIn0 to ANIn9 pins is defined

by a timer event signal (A/D converter trigger signal, or top and bottom reversal interrupt) of the inverter

timers R0 and R1 (TMR0, TMR1).

The analog input conversion timing is generated when an A/D converter trigger signal from the timers

(TR0ADTRG0, TR0ADTRG1, TR1ADTRG0, TR1ADTRG1), or a top or bottom reversal interrupt

(INTTR0CD, INTR0OD, INTTR1CD, INTTR1OD) is generated by inverter timer R0 or R1 (TMR0 or

TMR1).

When the ADCEn bit of the ADMn0 register is set to 1, the A/D converter waits for the signal

(TR0ADTRG0, TR0ADTRG1, TR1ADTRG0, TR1ADTRG1) or interrupt (INTTR0CD, INTR0OD,

INTTR1CD, INTTR1OD), and starts conversion when the timer event occurs (ADCSn bit of the ADMn0

register = 1). When conversion is finished, the converter waits for a timer event signal again (ADCSn bit

= 0).

If the timer event signal occurs during conversion, the conversion operation is executed from the

beginning again.

If data is written to the ADMn0 to ADMn2 registers during conversion, the conversion operation is

stopped and executed from the beginning again.

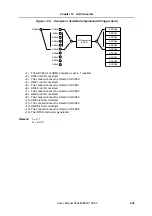

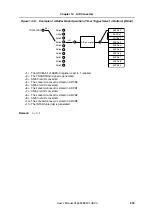

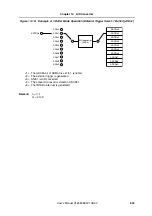

14.6.1 Select mode operation

In this mode, an analog input (ANIn0 to ANIn9) specified by the ADMn2 register is A/D converted. The

conversion results are stored in the ADCRnm register corresponding to the analog input. In the select

mode, the 1-buffer mode and 4-buffer mode are provided according to the storing method of the A/D

conversion results.

(1)

1-buffer mode operation (timer trigger select: 1 buffer)

In this mode, one analog input is A/D converted once and the conversion results are stored in one

ADCRnm register.

One analog input is A/D converted once using the trigger of the timer event signals (TR0ADTRG0,

TR0ADTRG1, TR1ADTRG0, TR1ADTRG1, INTTR0CD, INTR0OD, INTTR1CD, INTTR1OD) and

the results are stored in one ADCRnm register. An A/D conversion end interrupt (INTADn) is gen-

erated for each A/D conversion.

Unless the ADCEn bit of the ADMn0 register is cleared to 0, A/D conversion is repeated each time

a timer event signal is generated.

Содержание V850E/PH2

Страница 6: ...6 Preface User s Manual U16580EE3V1UD00...

Страница 16: ...16 User s Manual U16580EE3V1UD00...

Страница 28: ...28 User s Manual U16580EE3V1UD00...

Страница 32: ...32 User s Manual U16580EE3V1UD00...

Страница 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO...

Страница 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO...

Страница 192: ...192 Chapter 5 Memory Access Control Function PD70F3187 only User s Manual U16580EE3V1UD00 MEMO...

Страница 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO...

Страница 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00...

Страница 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO...

Страница 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00...

Страница 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO...

Страница 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO...

Страница 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO...

Страница 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO...

Страница 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO...

Страница 1052: ...1052 User s Manual U16580EE3V1UD00...

Страница 1053: ......