482

Chapter 11

16-bit Timer/Event Counter T

User’s Manual U16580EE3V1UD00

(5)

Overflow operation

Counter overflow occurs in the free-running mode, pulse width measurement mode, encoder

compare mode and offset trigger generation mode.

Overflow occurs when the counter value changes from FFFFH to 0000H.

In the free-running mode, pulse width measurement mode, offset trigger generation mode, the

overflow flag (TTnOVF) is set to 1 and an overflow interrupt (INTTTnOV) is output. At this time, the

TTnEOF flag is not set.

In the encoder compare mode, the encoder dedicated overflow flag (TTnEOF) is set to 1 and an

overflow interrupt (INTTTnOV) occurs. At this time, the TTnOVF flag is not set.

Under the following conditions, overflow does not occur.

•

When the counter value changes from initial setting FFFFH to 0000H immediately after

counting start

•

When FFFFH is set to the compare register, and the counter is cleared to 0000H upon a match

between the counter value and the compare setting value.

•

When, in the pulse width measurement mode and offset trigger generation mode, capture

operation is performed for counter value FFFFH, and the counter is cleared to 0000H.

(6)

Underflow operation

Counter underflow occurs in the triangular wave PWM Mode and encoder compare mode.

Underflow occurs when the counter value changes from 0000H to FFFFH.

When underflow occurs in the triangular wave PWM mode, an overflow interrupt (INTTTnOV)

occurs. At this time, the TTnOVF flag is not set.

In the encoder compare mode, the encoder dedicated underflow flag (TTnEUF) is set to 1, and an

overflow interrupt (INTTTnOV) occurs.

Underflow does not occur during count down immediately following counter start.

(7)

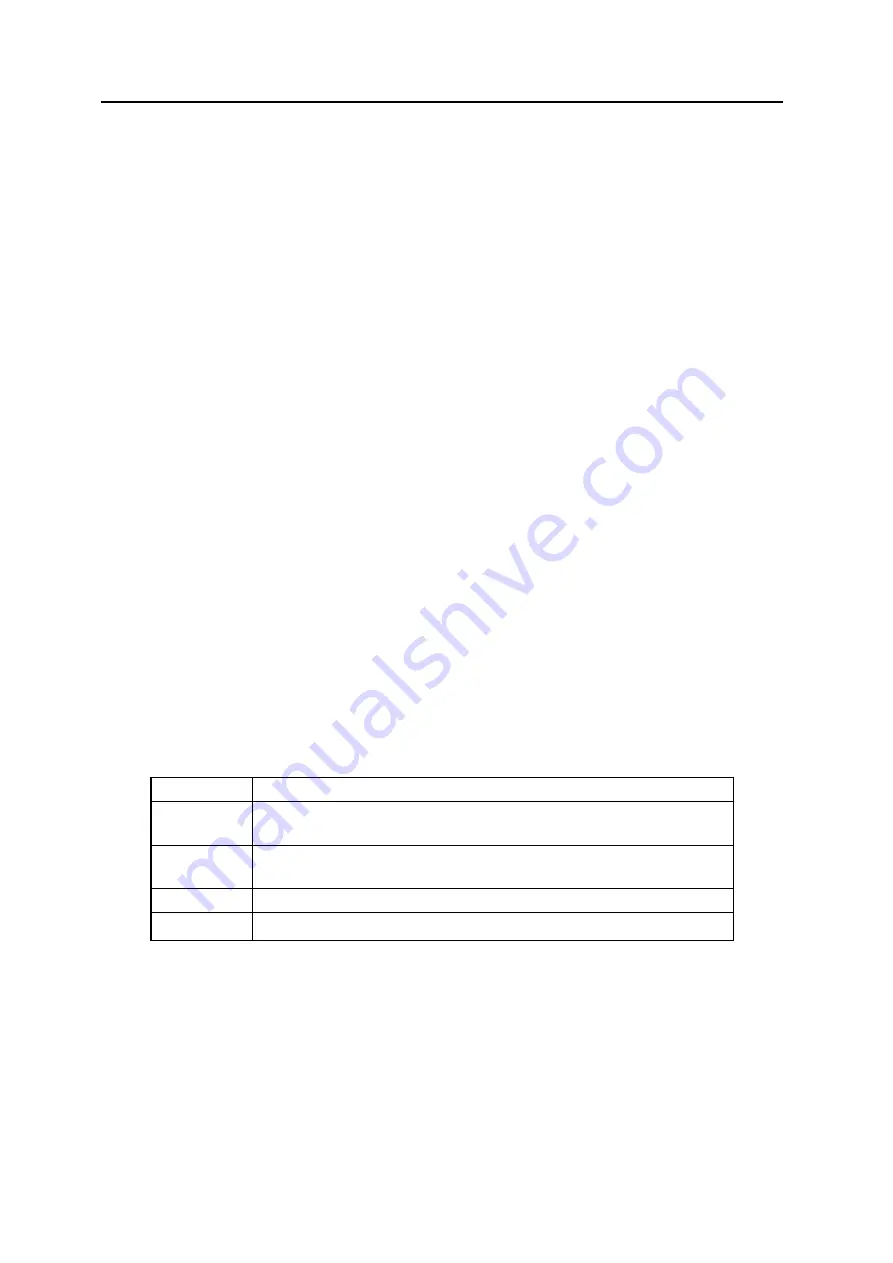

Description of interrupt signal operation

In TMT, the following interrupt signals are output.

Note:

In the encoder compare mode, when TTnSCE = 0, an encoder clear interrupt (INTTTnEC) is

output.

Remark:

n = 0, 1

Name

Occurrence Cause

INTTTnCC0

•

Match between counter and setting value of TTnCCR0 register

•

Capture to TTnCCR0 register due to TITn0 pin input

INTTTnCC1

•

Match between counter and setting value of TTnCCR1 register

•

Capture to TTnCCR1 register due to TITn1 pin input

INTTTnOV

Overflow and underflow occurrence

INTTTnEC

Note

Counter clearing through TECRTn pin

Содержание V850E/PH2

Страница 6: ...6 Preface User s Manual U16580EE3V1UD00...

Страница 16: ...16 User s Manual U16580EE3V1UD00...

Страница 28: ...28 User s Manual U16580EE3V1UD00...

Страница 32: ...32 User s Manual U16580EE3V1UD00...

Страница 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO...

Страница 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO...

Страница 192: ...192 Chapter 5 Memory Access Control Function PD70F3187 only User s Manual U16580EE3V1UD00 MEMO...

Страница 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO...

Страница 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00...

Страница 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO...

Страница 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00...

Страница 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO...

Страница 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO...

Страница 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO...

Страница 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO...

Страница 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO...

Страница 1052: ...1052 User s Manual U16580EE3V1UD00...

Страница 1053: ......