394

Chapter 10

16-bit Inverter Timer/Counter R

User’s Manual U16580EE3V1UD00

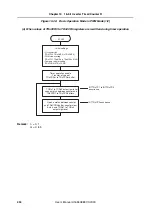

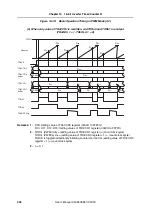

10.10.3 External trigger pulse output mode (TMR1 only)

(1)

Outline of external trigger pulse output mode

When, in the external trigger pulse mode, the duty is set to the TR1CCR1 to TR1CCR5 registers,

the cycle is set to the TR1CCR0 register, and TR1CE = 1 is set, external trigger input (TTRGR1

pin) wait results, with the counter remaining stopped at FFFFH. Upon detection of the valid edge

of external trigger input (TTRGR1 pin), or when the TR1EST bit of the TR1CTL1 register is set,

count up starts. An external trigger pulse is output from pins TOR11 to TOR15, and toggle output

is performed from pin TOR10 upon a match with the TR1CCR0 register. Moreover, during the

count operation, upon a match between the counter and the TR1CCR0 register, a compare match

interrupt (INTTR1CC0) is output, and upon a match between the counter and TR1CCR1 to

TR1CCR5 registers, compare match interrupts (INTTR1CC1 to INTTR1CC5) are output.

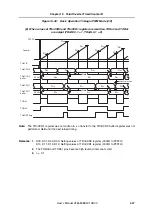

The TR1CCR0 to TR1CCR5 registers can be rewritten during count operation. Compare register

reload is performed at the timing when the counter value and the TR1CCR0 register match.

However, when write access to the TR1CCR1 register is performed, the next reload timing

becomes valid, so that even if wishing to rewrite only the value of the TR1CCR0 register, write the

same value to the TR1CCR1 register. In this case, reload is not performed even if only the

TR1CCR0 register is rewritten.

If, during operation in the external trigger pulse output mode, the external trigger (TTRGR1 pin)

edge is detected several times, or if the TR1EST bit of the TR1CTL1 register is set (to 1), the

counter is cleared and count up is resumed. Moreover, if at this time, the TOR11 to TOR15 pins

are in the low level status, the TOR11 to TOR15 pin outputs become high level when an external

trigger is input. If the TOR11 pin is in the high level status, it remains high level even if external

trigger input occurs.

In the external trigger pulse output mode, the TR1CCR0 to TR1CCR3 registers have their function

fixed as compare registers, so the capture function cannot be used.

Caution:

In the external trigger pulse mode, the external event clock input (TEVTR1) is prohib-

ited (TR1CTL1.TR1EEE = 0).

Содержание V850E/PH2

Страница 6: ...6 Preface User s Manual U16580EE3V1UD00...

Страница 16: ...16 User s Manual U16580EE3V1UD00...

Страница 28: ...28 User s Manual U16580EE3V1UD00...

Страница 32: ...32 User s Manual U16580EE3V1UD00...

Страница 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO...

Страница 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO...

Страница 192: ...192 Chapter 5 Memory Access Control Function PD70F3187 only User s Manual U16580EE3V1UD00 MEMO...

Страница 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO...

Страница 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00...

Страница 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO...

Страница 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00...

Страница 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO...

Страница 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO...

Страница 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO...

Страница 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO...

Страница 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO...

Страница 1052: ...1052 User s Manual U16580EE3V1UD00...

Страница 1053: ......