2-8

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

AACK_ and TA_ allows the PPC Slave to assert a retry to the processor in

the event that the transaction is unable to complete on the PCI side. It

should be noted that any transaction that crosses a PCI word boundary

could be disrupted after only having a portion of the data transferred.

The PPC Slave cannot perform compelled burst write transactions. The

PPC bus protocol mandates that the qualified retry window must occur no

later than the assertion of the first TA_ of a burst transaction. If the PHB

was to attempt a compelled linkage for all beats within a burst write, there

is a possibility that the transaction could be interrupted. The interruption

would occur at a time past the latest qualified retry window and the PPC

Slave would be unable to retry the transaction. Therefore, all burst write

transactions are posted regardless of the write posting attribute within the

associated map decoder register.

If the PPC Slave is servicing a posted write transaction and the PPC FIFO

can accept the transaction, the assertion of AACK_ and TA_ occurs as soon

as the PPC Slave decode logic settles out and the PPC bus protocol allows

for the assertion. If the PPC FIFO is full, the PPC Slave holds the processor

with wait states (AACK_ will not be asserted) until there is room within the

PPC FIFO to store the pending transaction.

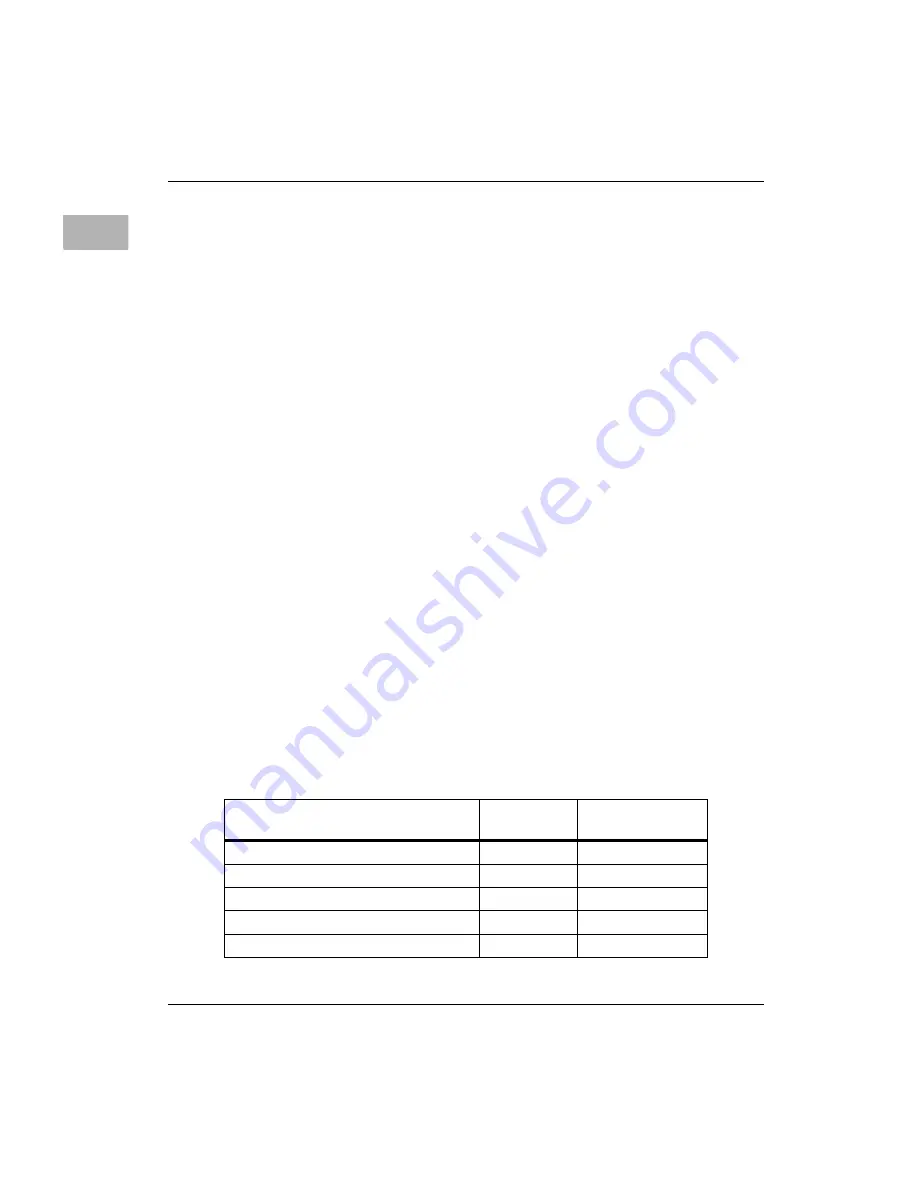

The PPC Slave divides PPC command types into three categories: address

only, write, and read. If a command type is an address only and the address

presented at the time of the command is a valid PHB address, the PPC

slave will respond immediately by asserting AACK_. The PHB will not

respond to address only cycles where the address presented is not a PHB

address. The response of the PPC Slave to command types is listed in

Table 2-1. PPC Slave Response Command Types

PPC Transfer Type

Transfer

Encoding

Transaction

Clean Block

00000

Addr Only

Flush Block

00100

Addr Only

SYNC

01000

Addr Only

Kill Block

01100

Addr Only

EIEIO

10000

Addr Only

Содержание MVME5100 Series

Страница 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Страница 16: ...xvi ...

Страница 20: ...xx ...

Страница 28: ...xxviii ...

Страница 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Страница 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Страница 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Страница 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...