2-44

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

The WDTxCNTL register will always become unarmed after the second

write regardless of byte lane selection. Reads may be performed at any

time from the WDTxCNTL register and will not affect the write arming

sequence The following example displays the PPCBug commands, which

arm, the disarm, the Watchdog timer 2.

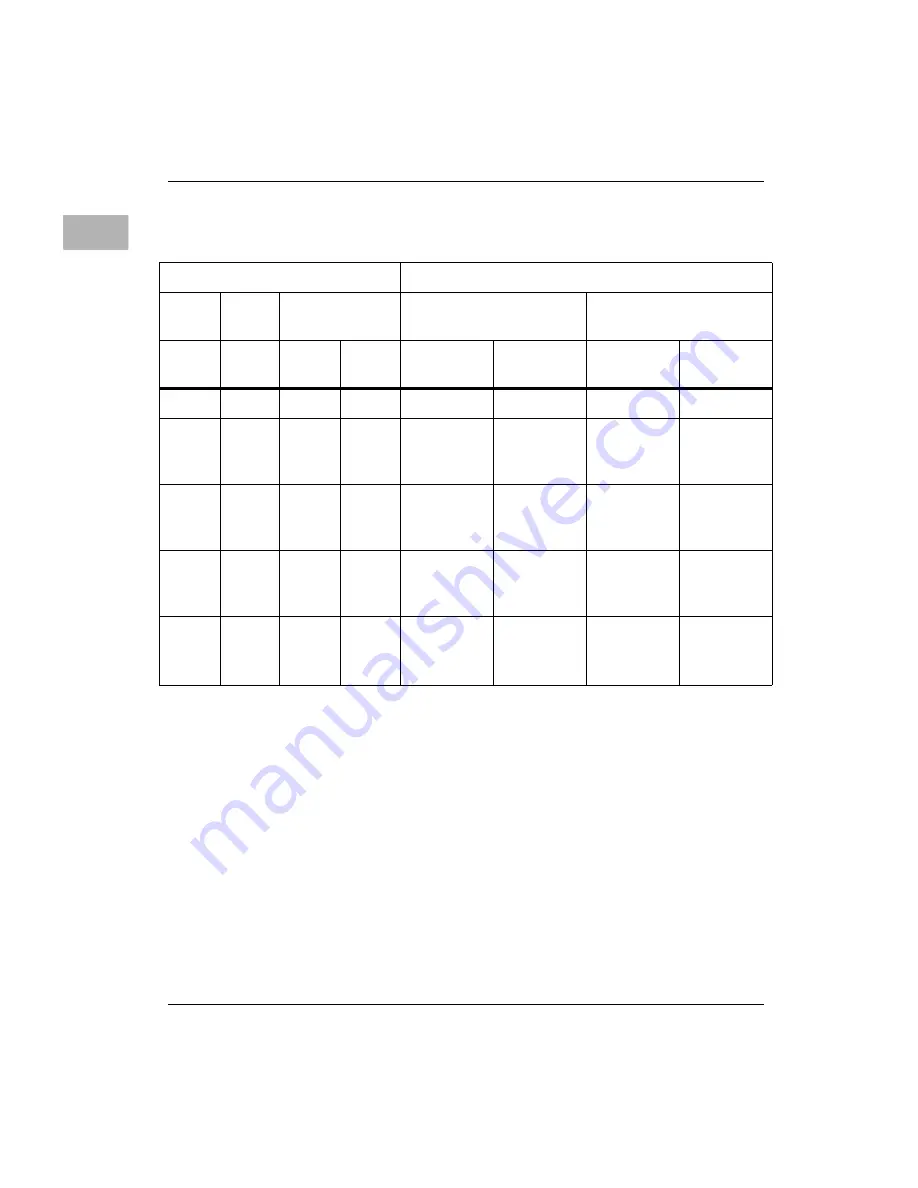

Table 2-14. WDTxCNTL Programming

Byte Lane Selection

Results

KEY

ENAB

/RES

RELOAD

WDT

WDTxCNTL Register

0:7

8:15

16:23

24:31

Prescaler/

Enable

Counter

RES/ENAB

RELOAD

No

x

x

x

No Change

No Change

No Change

No Change

Yes

No

x

x

Update

from

RES/ENAB

Update

from

RELOAD

No Change

No Change

Yes

Yes

No

x

Update

from data

bus

Update

from

RELOAD

Update

from data

bus

No Change

Yes

Yes

x

No

Update

from data

bus

Update

from

RELOAD

Update

from data

bus

No Change

Yes

Yes

Yes

Yes

Update

from data

bus

Update

from data

bus

Update

from data

bus

Update

from

data bus

Содержание MVME5100 Series

Страница 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Страница 16: ...xvi ...

Страница 20: ...xx ...

Страница 28: ...xxviii ...

Страница 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Страница 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Страница 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Страница 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...