Vital Product Data (VPD) Introduction

http://www.motorola.com/computer/literature

B-11

B

A product may contain multiple L2 cache configuration packets. This

product, the PPMCBASE, does not contain a L2 Cache device.

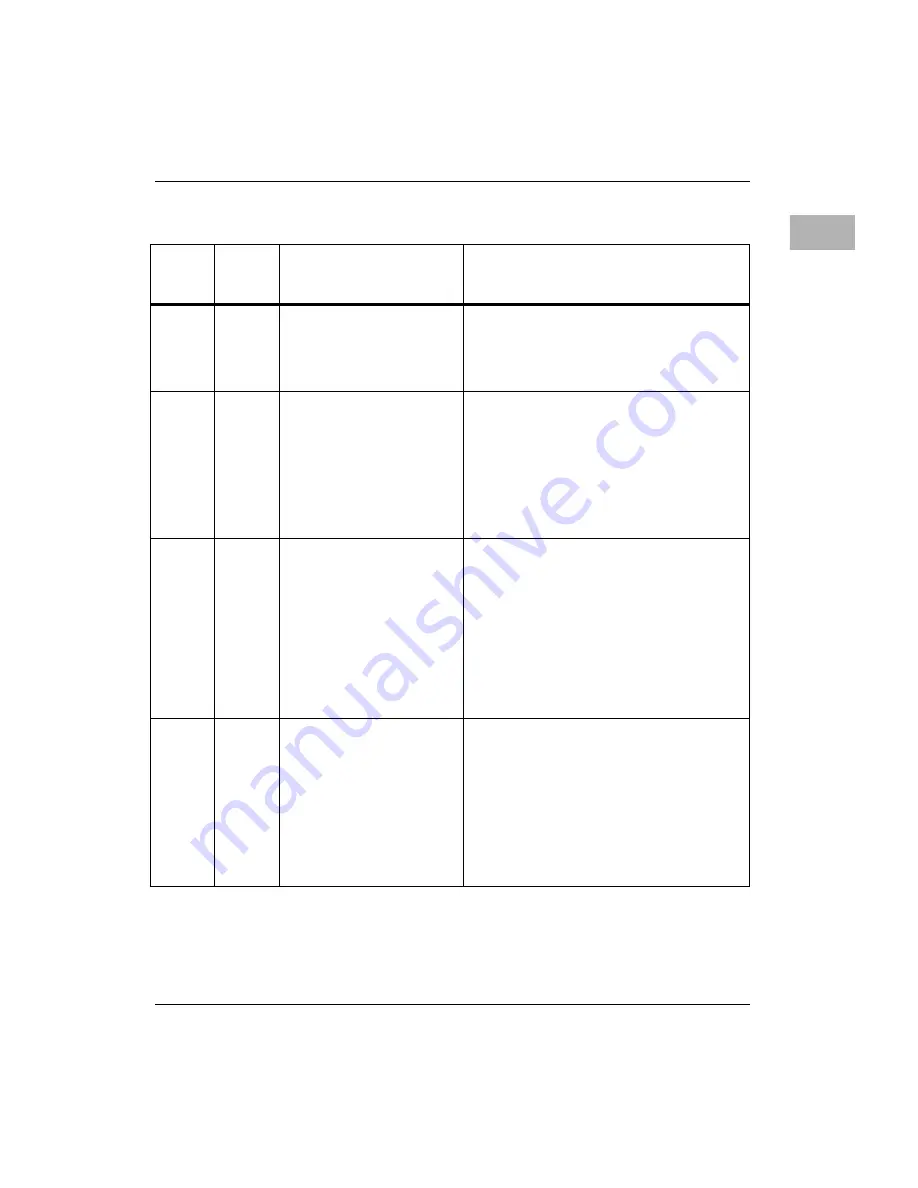

0B

1

L2C_ERROR_DETECT

Error Detection Type:

00 - None

01 - Parity

02 - ECC

0C

1

L2C_SIZE

L2 Cache Size (Should agree with the

physical organization above):

00 - 256K

01 - 512K

02 - 1M

03 - 2M

04 - 4M

0D

1

L2C_TYPE_BACKSIDE

L2 Cache Type (Backside Configurations):

00 - Late Write Sync, 1nS Hold, Differential

Clock, Parity

01 - Pipelined Sync Burst, 0.5nS Hold, No

Differentia Clock, Parity

02 - Late Write Sync, 1nS Hold, Differential

Clock, No Parity

03 - Pipelined Sync Burst, 0.5nS Hold, No

Differential Clock, No Parity

0E

1

L2C_RATIO_BACKSIDE

L2 Cache Core to Cache Ration (Backside

Configurations):

00 - Disabled

01 - 1:1 (1)

02 - 3:2 (1.5)

03 - 2:1 (2)

04 - 5:2 (2.5)

05 - 3:1 (3)

Table B-4. L2 Cache Configuration Data (Continued)

Byte

Offset

Field

Size

(Bytes)

Field Mnemonic

Field Description

Содержание MVME5100 Series

Страница 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Страница 16: ...xvi ...

Страница 20: ...xx ...

Страница 28: ...xxviii ...

Страница 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Страница 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Страница 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Страница 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...