2-120

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

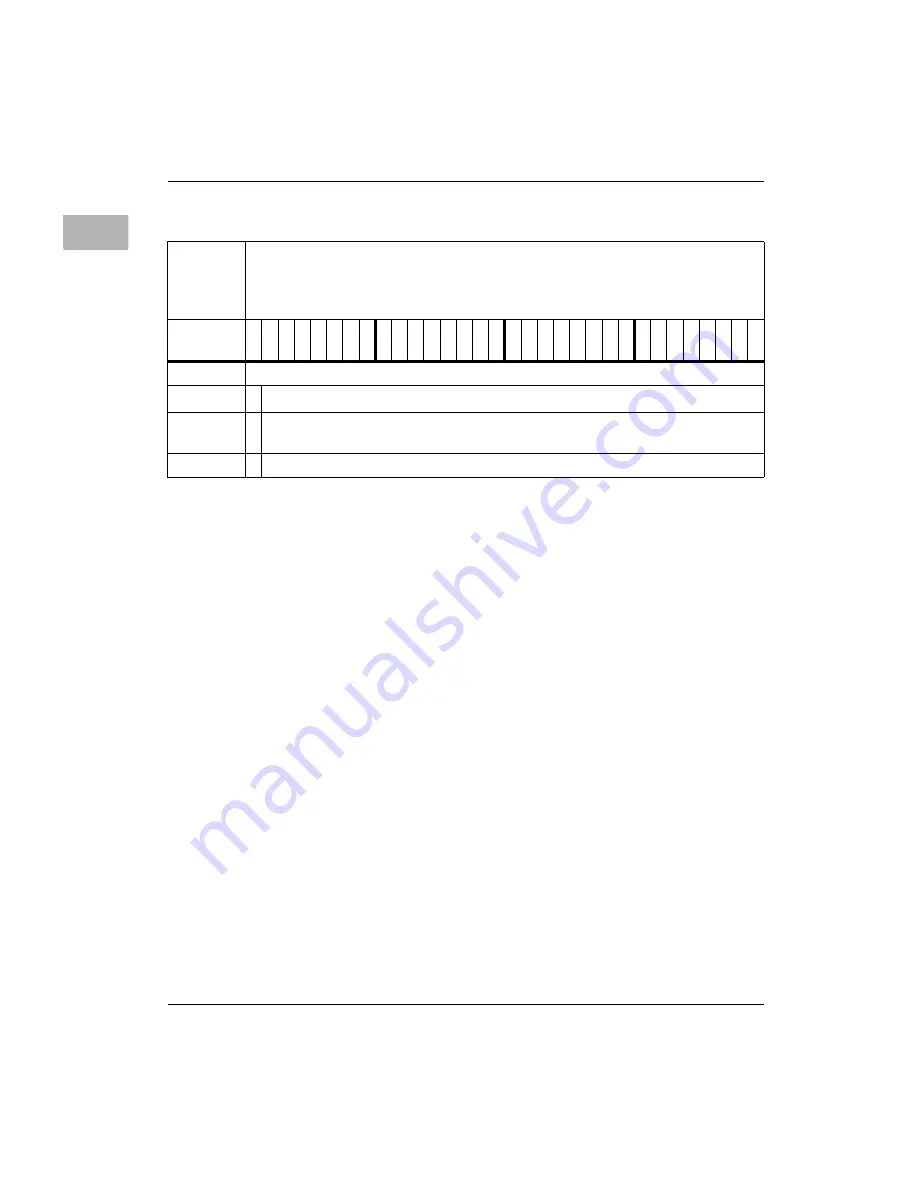

Timer Basecount Registers

CI

COUNT INHIBIT. Setting this bit to one inhibits counting

for this timer. Setting this bit to zero allows counting to

proceed.

BC

BASE COUNT. This field contains the 31 bit count for

this timer. When a value is written into this register and the

CI bit transitions from a 1 to a 0, it is copied into the

corresponding Current Count register and the toggle bit in

the Current Count register is cleared. When the timer

counts down to zero, the Current Count register is

reloaded from the Base Count register and the timer’s

interrupt becomes pending in MPIC processing.

Offset

Timer 0 - $01110

Timer 1 - $01150

Timer 2 - $01190

Timer 3 - $011D0

Bit

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Name

TIMER BASECOUNT

CI

BC

Operation

R/

W

R/W

Reset

1

$00000000

Содержание MVME5100 Series

Страница 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Страница 16: ...xvi ...

Страница 20: ...xx ...

Страница 28: ...xxviii ...

Страница 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Страница 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Страница 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Страница 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...