Registers

http://www.motorola.com/computer/literature

2-103

2

The MPIC Memory Base Address Register (MMBAR) controls the

mapping of the MPIC control registers in PCI memory space.

IO/MEM

IO Space Indicator. This bit is hard-wired to a logic zero

to indicate PCI memory space.

MTYPx

Memory Type. These bits are hard-wired to zero to

indicate that the MPIC registers can be located anywhere

in the 32-bit address space.

PRE

Prefetch. This bit is hard-wired to zero to indicate that the

MPIC registers are not prefetchable.

BASE

Base Address. These bits define the memory space base

address of the MPIC control registers. The MBASE

decoder is disabled when the BASE value is zero.

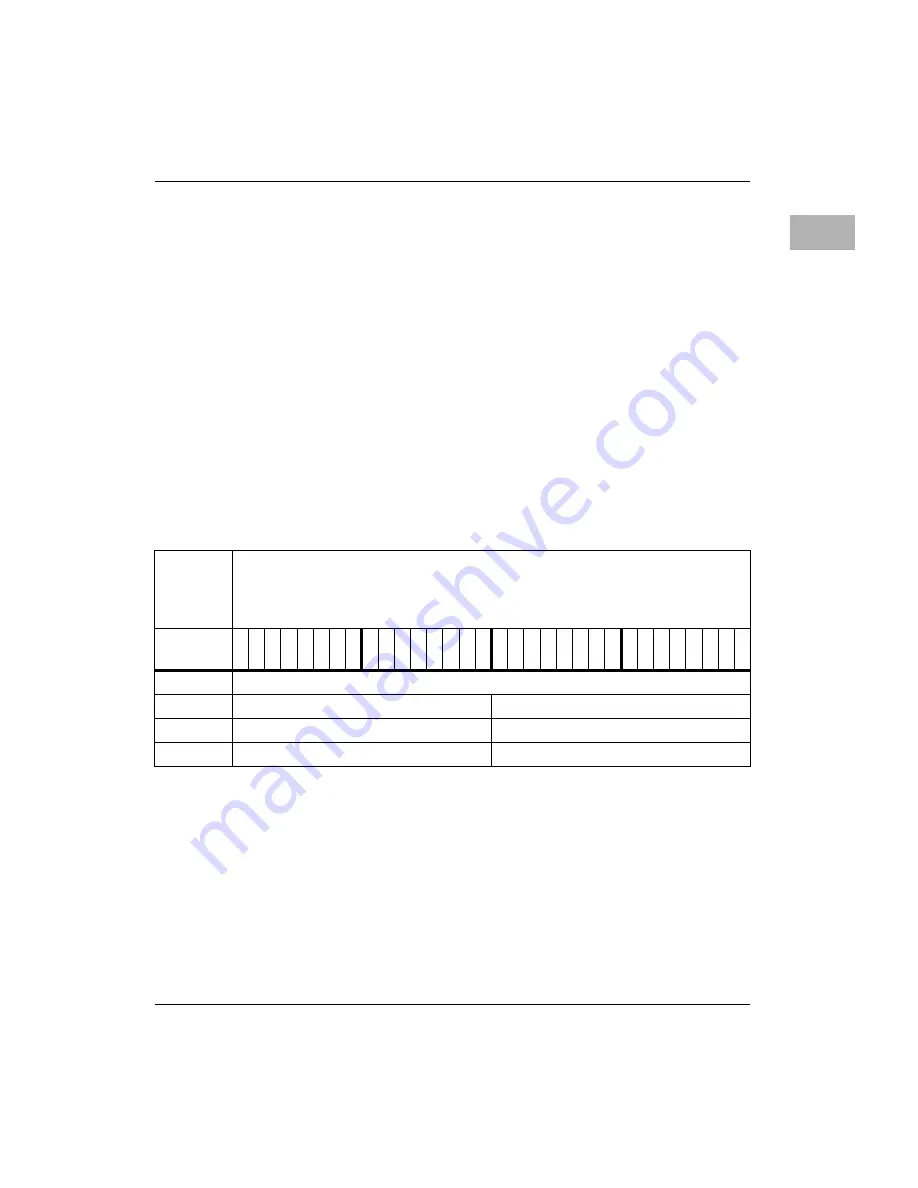

PCI Slave Address (0,1,2, and 3) Registers

Offset

PSADD0 - $80

PSADD1 - $88

PSADD2 - $90

PSADD3 - $98

Bit

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Name

PSADDx

START

END

Operation

R/W

R/W

Reset

$0000

$0000

Содержание MVME5100 Series

Страница 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Страница 16: ...xvi ...

Страница 20: ...xx ...

Страница 28: ...xxviii ...

Страница 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Страница 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Страница 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Страница 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...