2-74

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

PRI

Priority. If set, the PPC Arbiter will impose a rotating

between CPU0 grants. If cleared, a fixed priority will be

established between CPU0 and CPU1 grants, with CPU0

having a higher priority than CPU1.

PRKx

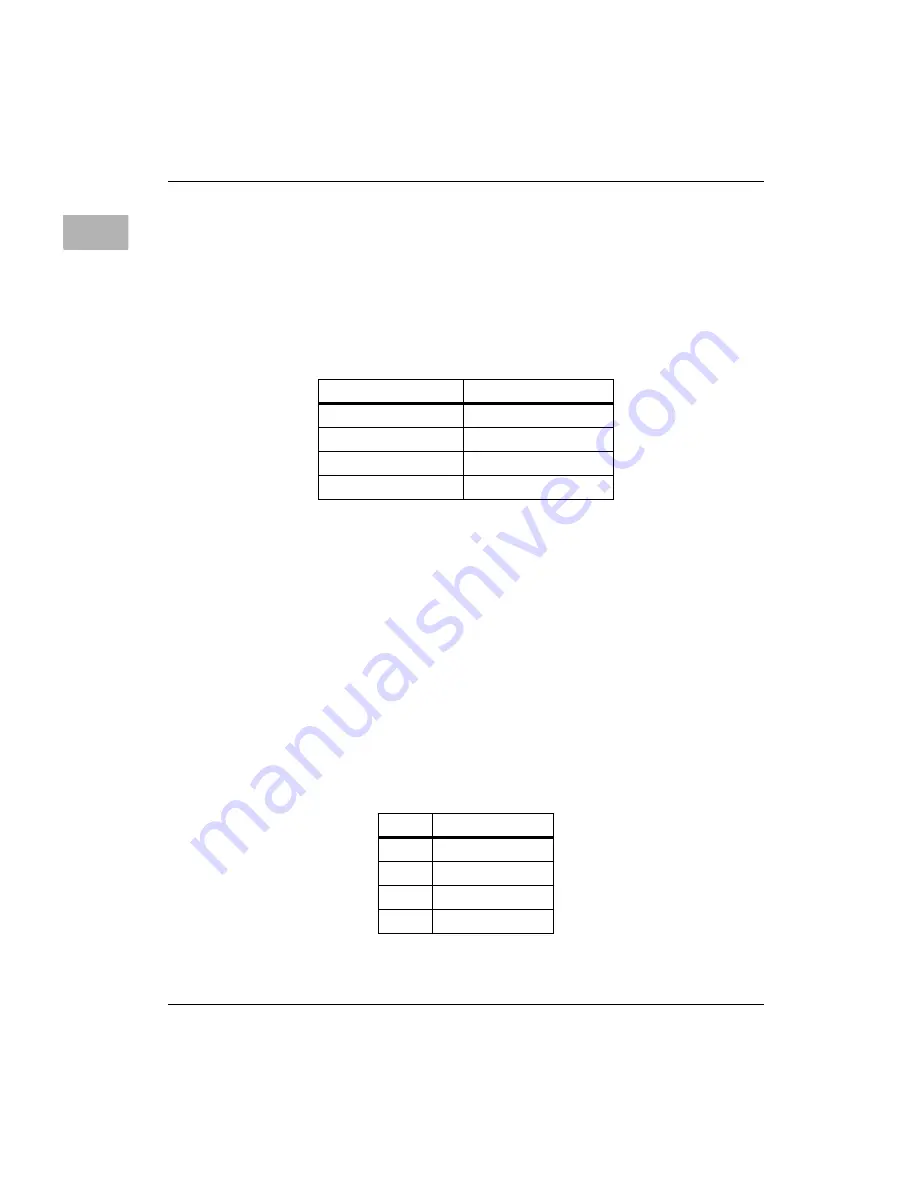

Parking. This field determines how the PPC Arbiter will

implement CPU parking. The encoding of this field is

shown in the table below.

ENA

Enable. This read only bit indicates the enabled state of

the PPC Arbiter. If set, the PPC Arbiter is enabled and is

acting as the system arbiter. If cleared, the PPC Arbiter is

disabled and external logic is implementing the system

arbiter. Refer to the section titled

for more information on how this bit gets

set.

The PCI Arbiter Register (PARB) provides control and status for the PCI

Arbiter. Refer to the section titled

for more informatiion. The

bits within the PARB register are defined as follows:

PRIx

Priority. This field is used by the PCI Arbiter to establish

a particular bus priority scheme. The encoding of this field

is shown in the following table.

PRK

CPU Parking

00

None

01

Park on last CPU

10

Park always on CPU0

11

Park always on CPU1

PRI

Priority Scheme

00

Fixed

01

Round Robin

10

Mixed

11

Reserved

Содержание MVME5100 Series

Страница 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Страница 16: ...xvi ...

Страница 20: ...xx ...

Страница 28: ...xxviii ...

Страница 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Страница 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Страница 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Страница 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...