Programming Model

http://www.motorola.com/computer/literature

3-55

3

rom_a_rv is initialized at power-up reset to match the

value on the RD0 pin.

rom a en

When rom a en is set, accesses to Block A ROM/Flash in

the address range selected by ROM A BASE are enabled.

When rom a en is cleared, they are disabled.

rom a we

When rom a we is set, writes to Block A ROM/Flash are

enabled. When rom a we is cleared, they are disabled.

Note that if rom_a_64 is cleared, only 1-byte writes are

allowed. If rom_a_64 is set, only 4-byte writes are

allowed. The SMC ignores other writes. If a valid write is

attempted and rom a we is cleared, the write does not

happen but the cycle is terminated normally.

See

for details of ROM/Flash accesses.

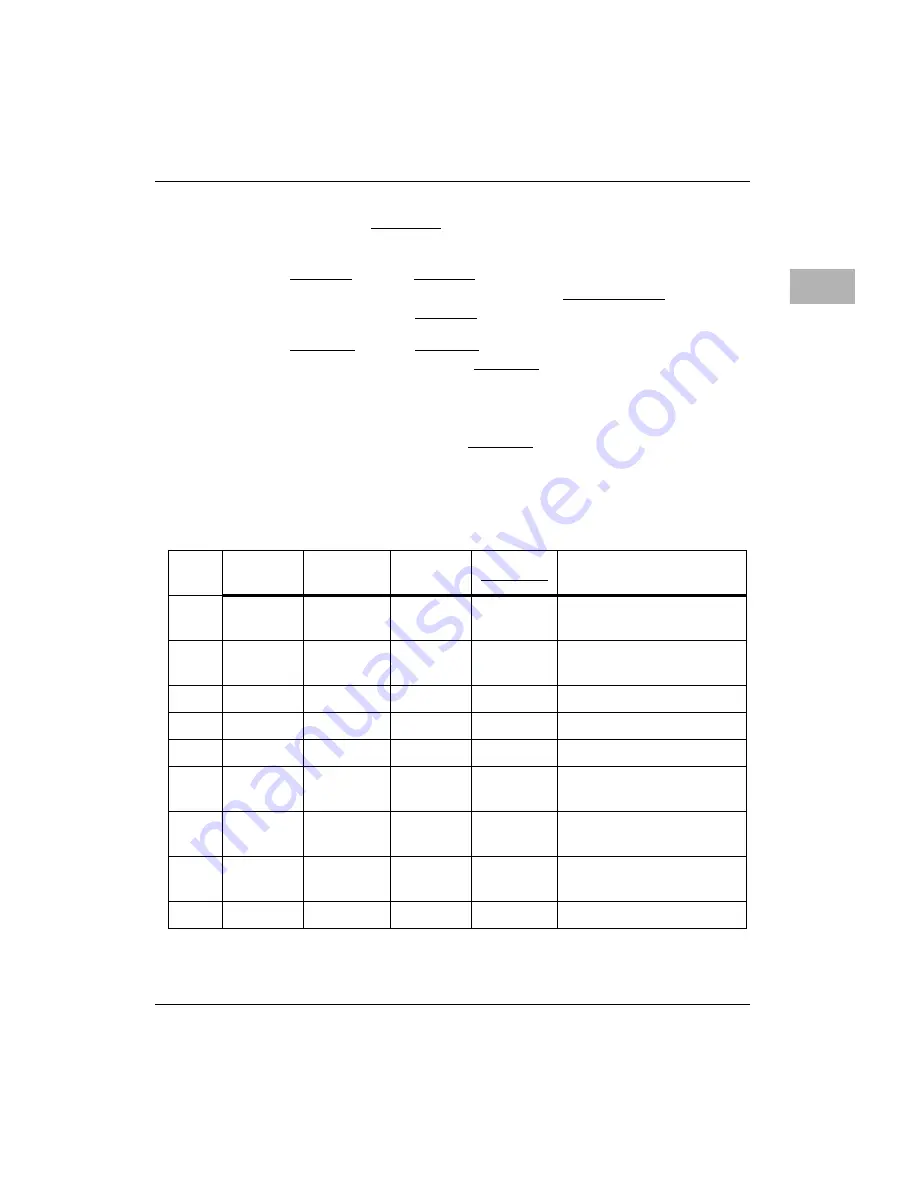

Table 3-13. Read/Write to ROM/Flash

Cycle

Transfer

Size

Alignment

rom_x_64

rom_x_we

Hawk Response

write

1-byte

X

0

0

Normal termination, but no

write to ROM/Flash

write

1-byte

X

0

1

Normal termination, write

occurs to ROM/Flash

write

1-byte

X

1

X

No Response

write

4-byte

Misaligned

X

X

No Response

write

4-byte

Aligned

0

X

No Response

write

4-byte

Aligned

1

0

Normal termination, but no

write to ROM/Flash

write

4-byte

Aligned

1

1

Normal termination, write

occurs to ROM/Flash

write

2,3,5,6,7,

8,32-byte

X

X

X

No Response

read

X

X

X

X

Normal Termination

Содержание MVME5100 Series

Страница 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Страница 16: ...xvi ...

Страница 20: ...xx ...

Страница 28: ...xxviii ...

Страница 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Страница 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Страница 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Страница 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...