2-92

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

The PPC Slave Attributes Register 3 (XSATT3) contains attribute

information associated with the mapping of PPC memory space to PCI I/O

space. The bits within the XSATT3 register are defined as follows:

REN

Read Enable. If set, the corresponding PPC Slave is

enabled for read transactions.

WEN

Write Enable. If set, the corresponding PPC Slave is

enabled for write transactions.

WPEN

Write Post Enable. If set, write posting is enabled for the

corresponding PPC Slave.

IOM

PCI I/O Mode. If set, the corresponding PPC Slave

generates PCI I/O cycles using spread addressing as

defined in the section on

. When

clear, the corresponding PPC Slave generates PCI I/O

cycles using contiguous addressing.

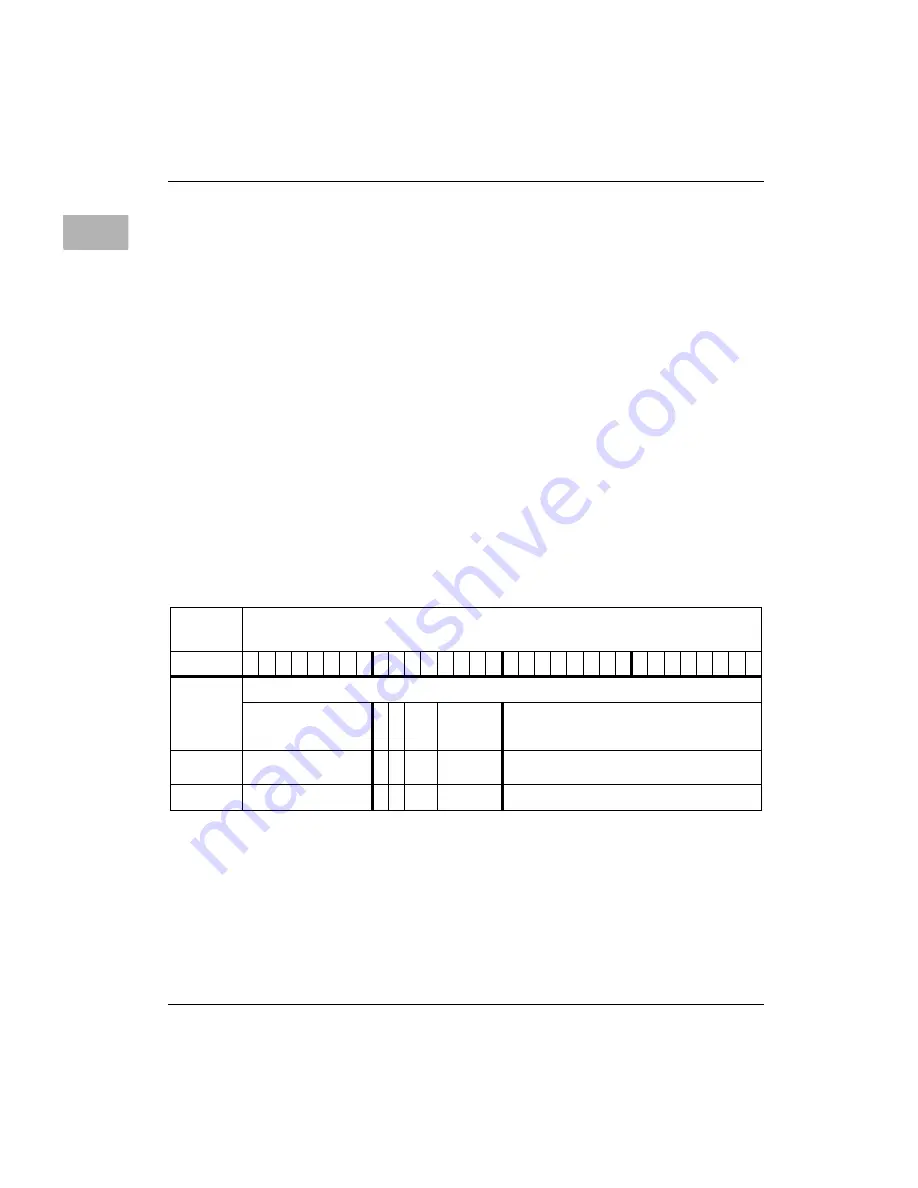

WDTxCNTL Registers

The Watchdog Timer Control Registers (WDT1CNTL and

WDT2CNTL) are used to provide control information to the watchdog

timer functions within the PHB. The fields within WDTxCNTL registers

are defined as follows:

Address

WDT1CNTL - $FEFF0060

WDT2CNTL - $FEFF0068

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

WDTxCNTL

KEY

ENAB

ARM

RES

RELOAD

Operation

W

R/

W

R

R

R/W

R/W

Reset

$00

1

0

00

$7 or $8

$FF

Содержание MVME5100 Series

Страница 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Страница 16: ...xvi ...

Страница 20: ...xx ...

Страница 28: ...xxviii ...

Страница 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Страница 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Страница 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Страница 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...