Registers

http://www.motorola.com/computer/literature

2-125

2

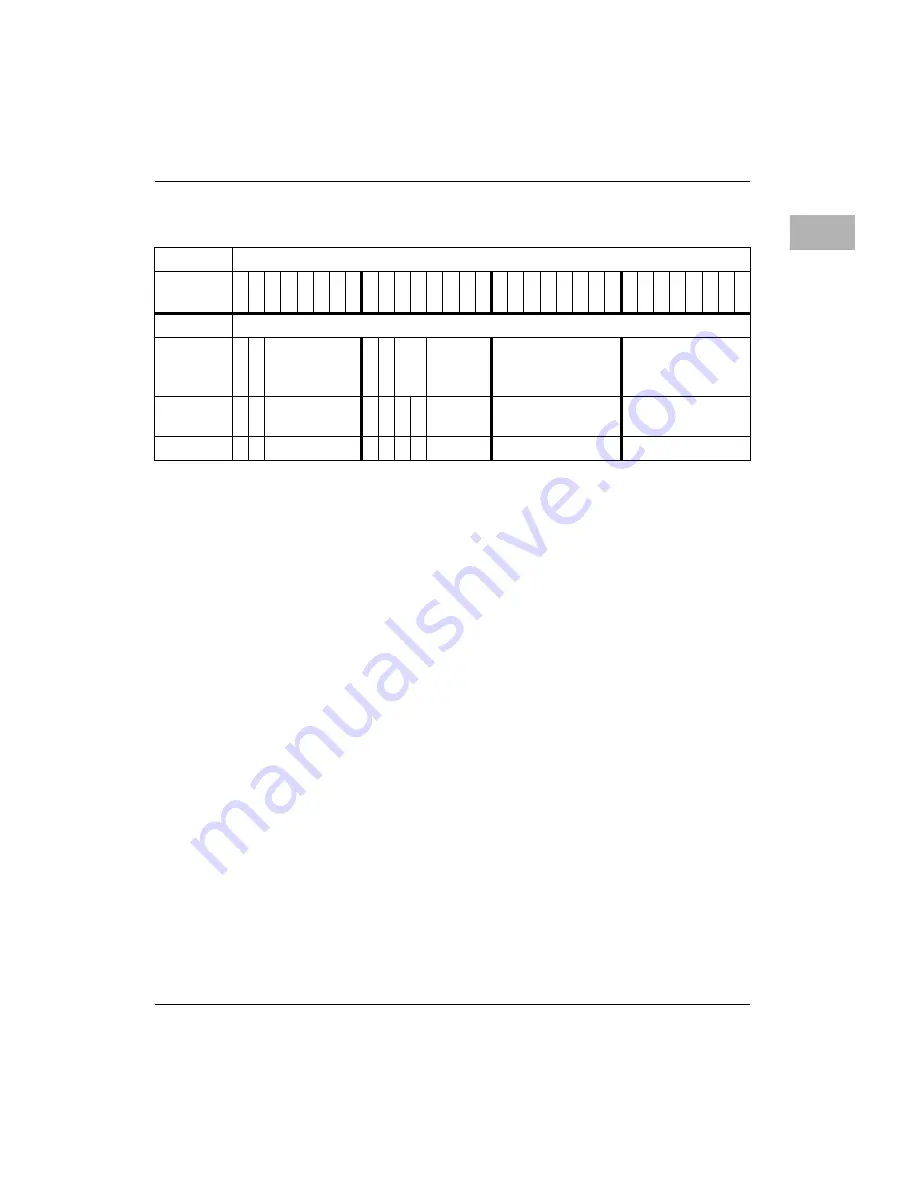

Hawk Internal Error Interrupt Vector/Priority Register

MASK

MASK. Setting this bit disables any further interrupts

from this source. If the mask bit is cleared, while the bit

associated with this interrupt is set in the IPR, the interrupt

request will be generated.

ACT

ACTIVITY. The activity bit indicates that an interrupt has

been requested or that it is in-service. The ACT bit is set

to one when its associated bit in the Interrupt Pending

Register or In-Service Register is set.

SENSE

SENSE. This bit sets the sense for Hawk’s internal error

interrupt. It is hardwired to 1 to enable active low level

sensitive interrupts.

PRIOR

PRIORITY. Interrupt priority 0 is the lowest and 15 is the

highest. Note that a priority level of 0 will not enable

interrupts.

VECTOR VECTOR. This vector is returned when the Interrupt

Acknowledge register is examined upon acknowledgment

of the interrupt associated with this vector.

Offset

$10200

Bit

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Name

HAWK INTERNAL ERROR INTERRUPT VECTOR/PRIORITY

MAS

K

AC

T

SE

NS

E

PRIOR

VECTOR

Operation

R/

W

R

R

R

R

R

R

R/W

R

R/W

Reset

1

0

$000

0

1

0

0

$0

$00

$00

Содержание MVME5100 Series

Страница 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Страница 16: ...xvi ...

Страница 20: ...xx ...

Страница 28: ...xxviii ...

Страница 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Страница 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Страница 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Страница 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...