Programming Model

http://www.motorola.com/computer/literature

3-69

3

cl3

When cl3 is cleared, the SMC assumes that the SDRAM runs

with a CAS_ latency of 2. When cl3 is set, the SMC assumes that

it runs with a CAS_ latency of 3. Note that writing so as to

change cl3 from 1 to 0 or vice-versa causes the SMC to perform

a mode-register-set operation to the SDRAM array. The mode-

register-set operation updates the SDRAM’s CAS latency to

match cl3.

trc0,1,2

Together trc0,1,2 determine the minimum number of clock

cycles that the SMC assumes the SDRAM requires to satisfy its

Trc parameter. These bits are encoded as follows:

tras0,1

Together tras0,1 determine the minimum number of clock

cycles that the SMC assumes the SDRAM requires to satisfy its

tRAS parameter. These bits are encoded as follows:

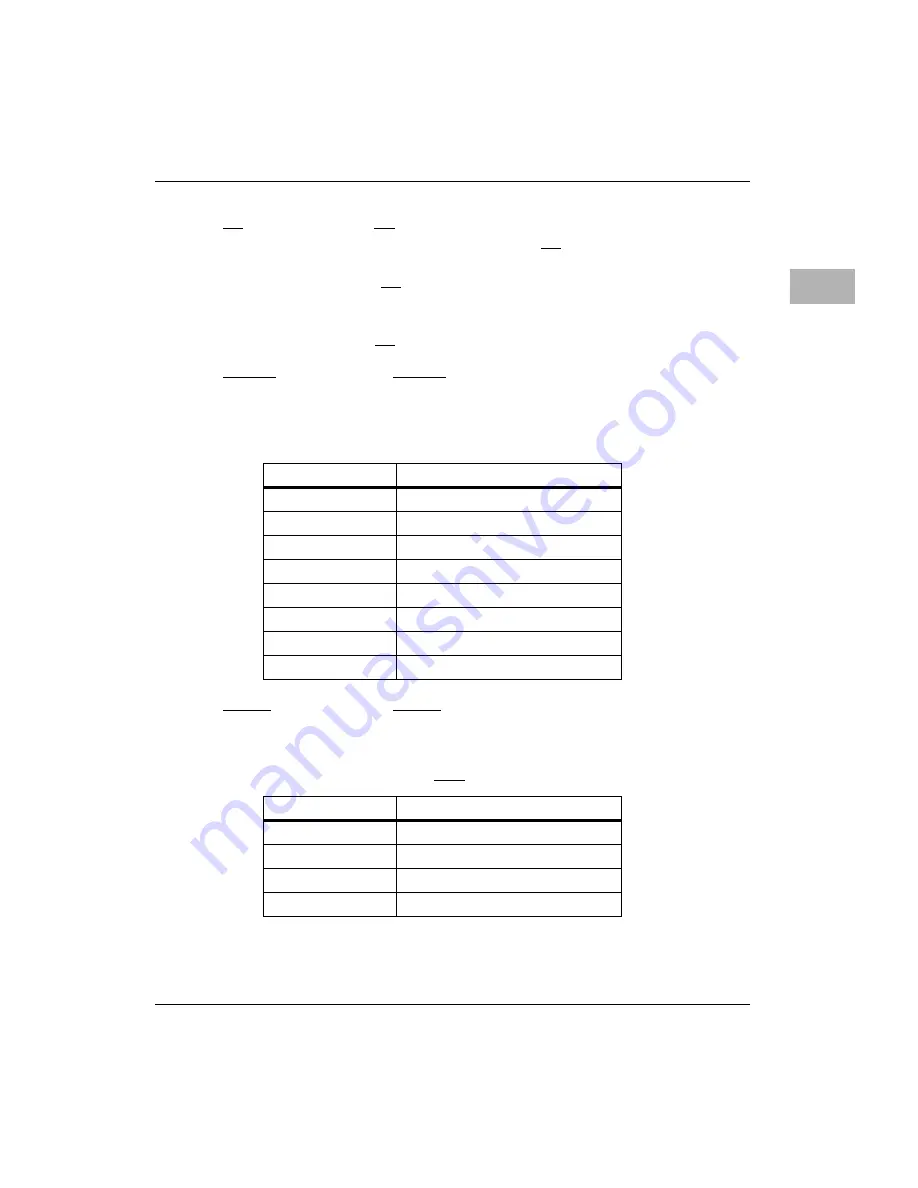

Table 3-16. Trc Encoding

trc0,1,2

Minimum Clocks for Trc

%000

8

%001

9

%010

10

%011

11

%100

reserved

%101

reserved

%110

6

%111

7

Table 3-17. tras Encoding

tras0,1

Minimum Clocks for tras

%00

4

%01

5

%10

6

%11

7

Содержание MVME5100 Series

Страница 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Страница 16: ...xvi ...

Страница 20: ...xx ...

Страница 28: ...xxviii ...

Страница 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Страница 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Страница 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Страница 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...