ADwin-Pro

Hardware, manual version 2.9, June 2006

167

Pro I: Signal Conditioning and Interface Modules

Pro-LPSH-4-FI Rev. A, Pro-LPSH-8-FI Rev. A

ADwin

5.9.4 Pro-LPSH-4-FI Rev. A, Pro-LPSH-8-FI Rev. A

The module Pro-LPSH-4-FI Rev. A has 4 low-pass filters of 4th order with

Sample & Hold and isolation amplifiers, the module Pro-LPSH-8-FI Rev. A has

8 of these low-pass filters. The filters are Butterworth filters with a fixed cut-off

frequency. The frequency has to be indicated when you place an order. The

inputs are all optically isolated from system circuitry and from each other.

A low-pass filter module has to be used in combination with an analog input

module. (Pro-AIn-8/12 or Pro-AIn-8/16). A low-pass filter module and an ana-

log input module are then forming one unity, which is 2 inches (10 HP) wide

and therefore needs two slots.

The switching from sample to hold mode has to be made by the instruction

SH_SETMODE(module,mode)

.

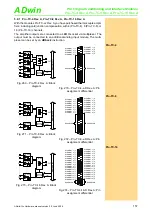

Fig. 295 – Pro-LPSH-8-FI Rev. A in combination with Pro-AIN-8/12 Rev. A

Input channels

4 at Pro-LPSH-4-FI Rev. A, isolated

8 bei Pro-LPSH-8-FI Rev. A, isolated

Input voltage range

±10V

Isolation voltage

1kV

Offset drift

40 ppm/°C

Non-linearity

0.016%

Input resistance

100k

Ω

Filter

Butterworth 4

th

order

Cut-off frequency

5kHz, 10kHz, 20kHz

(other frequencies on request)

Cut-off frequency error

±5%

Sample & Hold drift

1.5mV/s

Linearity

±1 LSB (12 bit)

Connector

4 / 8 LEMO sockets

(optional: 37-pin DSub socket)

Fig. 296 – Pro-LPSH-4/8-FI Rev. A: Specification

MUX

addr.

data

data

register

address

decoder

1

. . .

. .

A

D

10

0k

LPF

ISO

2

10

0k

LPF

ISO

8

10

0k

LPF

ISO

. . .

. .

. . .

. .

. . .

. .

PGA

S&H

S&H

S&H

ADwi

n

-P

ro

bu

s

. .

.

. .