2. PCI Interface

62

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

2.6

I

2

O Shell Interface

PowerSpan II provides portions of the I

2

O Shell Interface for the platform it is connecting to the

Primary PCI bus. The I

2

O Shell Interface defined in the

I

2

O 2.0 Specification

is comprised of three

main sections:

•

messaging interface

•

protocol for exchanging messages

•

executive class messages

PowerSpan II implements the I

2

O messaging interface and, in conjunction with the Input/Output

Processor (IOP), enables the message passing protocol.

2.6.1

I

2

O Target Image

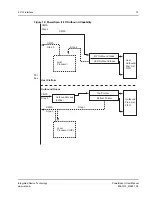

There are three registers which enable Memory access to the I

2

O Shell Interface and local IOP

Message Frames. The supporting registers include the following:

•

“PCI-1 I2O Target Image Base Address Register” on page 257

•

“PCI I2O Target Image Control Register” on page 352

•

“PCI I2O Target Image Translation Address Register” on page 356

The I

2

O Shell Interface consists of Inbound and Outbound Queues and supporting I

2

O Host interrupt

registers. The queues contain Message Frame Addresses (MFAs). These MFAs specify the starting

address of Message Frames relative to the base address of the memory window in PowerPC memory.

PowerSpan II implements I

2

O support with the first Memory Base Address Register in PCI

configuration space.

The I

2

O target image is divided into an I

2

O Shell Interface and a processor bus memory window

intended for IOP Message Frame accesses. The I

2

O Shell Interface is accessed through the lower 4

Kbytes of the I

2

O target image. I

2

O Shell Interface accesses are limited to 32-bit single data phase PCI

transactions. Accesses through the I

2

O target image memory window to IOP Message Frames are

burstable up to 64-bits wide for PCI-1, but limited to 32-bit wide for PCI-2.

PowerSpan II does not support posting of more than one write transaction to the Inbound or Outbound

Queue. Attempts to write to the Inbound or Outbound Queue are retried until the currently active write

completes on the Processor Bus Interface.

The I

2

O target image does not support Master-Based Decode.

Содержание PowerSpan II

Страница 8: ...Contents 8 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 14: ...List of Tables 14 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 18: ...About this Document 18 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 82: ...2 PCI Interface 82 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 112: ...3 Processor Bus Interface 112 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 156: ...7 Interrupt Handling 156 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 380: ...12 Register Descriptions 380 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 394: ...14 Package Information 394 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 414: ...15 AC Timing 414 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 416: ...16 Ordering Information 416 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 420: ...A Hardware Implementation 420 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 428: ...B Typical Applications 428 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 432: ...Glossary 432 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...