12. Register Descriptions

300

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

12.5.29

Processor Bus to PCI-1 Interrupt Acknowledge Cycle Generation Register

This register is used to generate an Interrupt Acknowledge cycle originating on the Processor Bus and

destined for the PCI-1 bus. Reading this register from the Processor Bus causes an IACK cycle to be

generated on the PCI bus. The byte lanes enabled on the PCI bus are determined by PB_SIZ[0:3] and

PB_A[30:31] of the Processor Bus read cycle. The address on the Processor Bus used to access the

PB_P1_IACK register is passed directly over to the PCI bus during the PCI IACK cycle. However,

address information is ignored during PCI IACK cycles, so this has no effect.

If the Address Retry Enable (ARTRY_EN) bit is set, in the

“PCI-1 Miscellaneous 1 Register” on

, the Processor Bus Master is retried until the read data is latched from the PCI target. When

the IACK cycle completes on the PCI-1 bus, the IACK_VEC[31:0] field is returned as read data when

the Processor Bus Master returns after the retry.

Writing to this register from the Processor Bus or either PCI bus has no effect. Reads from the PCI bus

return all zeros.

The END bit in the

“Processor Bus Register Image Base Address Register” on page 295

selects the

endian conversion scheme used for accesses to PCI through this register. The definition of endian

conversion scheme is for PCI accesses, not register accesses.

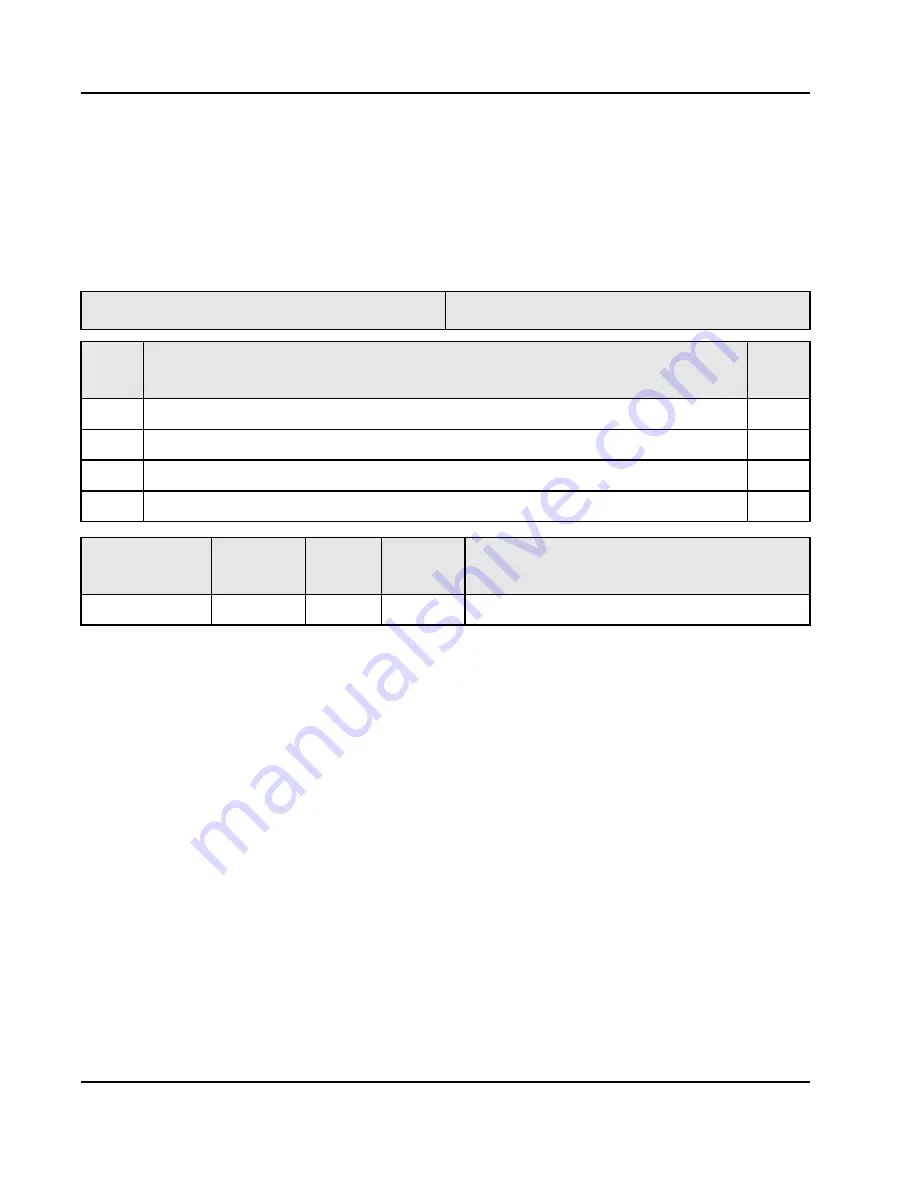

Register Name: PB_P1_IACK

Register Offset: 0x2A0

PCI

Bits

Function

PB

Bits

31-24

IACK_VEC

0-7

23-16

IACK_VEC

8-15

15-08

IACK_VEC

16-23

07-00

IACK_VEC

24-31

Name

Type

Reset

By

Reset

State

Function

IACK_VEC[31:0]

R

PB_RST

0

PCI IACK Cycle Vector

Содержание PowerSpan II

Страница 8: ...Contents 8 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 14: ...List of Tables 14 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 18: ...About this Document 18 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 82: ...2 PCI Interface 82 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 112: ...3 Processor Bus Interface 112 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 156: ...7 Interrupt Handling 156 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 380: ...12 Register Descriptions 380 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 394: ...14 Package Information 394 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 414: ...15 AC Timing 414 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 416: ...16 Ordering Information 416 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 420: ...A Hardware Implementation 420 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 428: ...B Typical Applications 428 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 432: ...Glossary 432 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...