A. Hardware Implementation

419

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

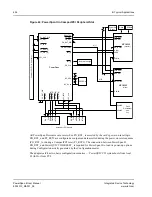

A.3.2

PowerSpan II External PLL Decoupling for New Designs

To provide the cleanest possible supply environment for the PLL, the supplies should be decoupled

externally. Isolation should be provided between the external core supply voltage on the board and the

supply that goes to the PLL. This can be done in the following ways:

•

A separate core voltage regulator can be provided and a separate trace run up to the PLL supply

pins.

•

An isolation and decoupling network can be provided for on the board to isolate and minimize

noise on the core voltage supply plane before it gets to the PLL supply pins.

For optimum PLL jitter performance, the PLL should be isolated and decoupled from the main core

power plane using a surface mount RF inductor and low ESR tantalum surface mount capacitor

network is recommended. The power supplies for PLLs on a device should come from a single point on

the board. The power trace should then be isolated from the main power plane using the network

shown in

.

The routing parasitic resistance of the trace route from any PLL supply pin to the decoupling capacitors

in the isolation network must be less than 0.1 Ohms. To minimize the transient IR drops across the

leads from the isolation network and the PLL supply device pins, the trace routes must be kept short.

The preferred layout is to have the cripple capacitors, shown in

, placed as close

to the device pins as possible; potentially on the backside of the board underneath the device.

Figure 42: PLL Decoupling

.0.5 Ohms(MIn)

4 Ohms(Max)

Cfilter

4.7uF(Min)

33uF(Max)

Lfilter

470nH(Min)

4.7uH(Min)

(RF SMT)

PowerSpan II

PLL_AVDD

PLL_DVDD

Cripple2

0.1uF

PLL_DVSS

PLL_AVSS

Core VDD

The VDD to VSS 0.1uF decoupling caps

must be as close to the device pins as possible.

Capacitors should be Low ESR (High Frequency)

ceramic chip capacitors.

The trace routing and

the Rdc of the inductor accounts

for this resistance and should be

in the range shown.

The trace routing

resistance must be

less than 0.1Ohms to Cripple1

and Cripple2.

Cfilter must be a

low ESR Tantalum

SMT capacitor.

Lfilter must

be a high SRF

SMT Wire wound

RF inductor.

Cripple1

0.1uF

Содержание PowerSpan II

Страница 8: ...Contents 8 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 14: ...List of Tables 14 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 18: ...About this Document 18 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 82: ...2 PCI Interface 82 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 112: ...3 Processor Bus Interface 112 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 156: ...7 Interrupt Handling 156 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 380: ...12 Register Descriptions 380 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 394: ...14 Package Information 394 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 414: ...15 AC Timing 414 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 416: ...16 Ordering Information 416 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 420: ...A Hardware Implementation 420 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 428: ...B Typical Applications 428 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 432: ...Glossary 432 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...