2. PCI Interface

40

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

Master-based Decode

The PCI Target supports Master-based decode when the PowerSpan II PCI arbiter is enabled (see

). With Master-based decode enabled, a PCI target image only claims a

transaction decoded for its specified physical address space if it originates from a specific PCI master.

External bus masters are selected for a specific target image by setting the corresponding bits in the

“PCI-1 Target Image x Translation Address Register” on page 274

2.2.1.2

Address Translation

The address generated on the destination port is dependent on the use of address translation in the

source target image. For more information, see the Translation Address Enable (TA_EN) bit in the

“PCI-1 Target Image x Control Register” on page 268

. When address translation is enabled

—

by

setting the TA_EN bit

—

the address generated on the destination bus is derived from the following

three inputs:

•

incoming address on the PCI Target

•

block size of the target image

BS[3:0] in the

“PCI-1 Target Image x Control Register” on page 268

•

translation address

TADDR in the

“PCI-1 Target Image x Translation Address Register” on page 274

When address translation is disabled the address on the destination bus is the same as the address on the

source bus.

2.2.1.3

Transaction Type Mapping

A transaction can be mapped to the PB interface or to another PCI Interface.

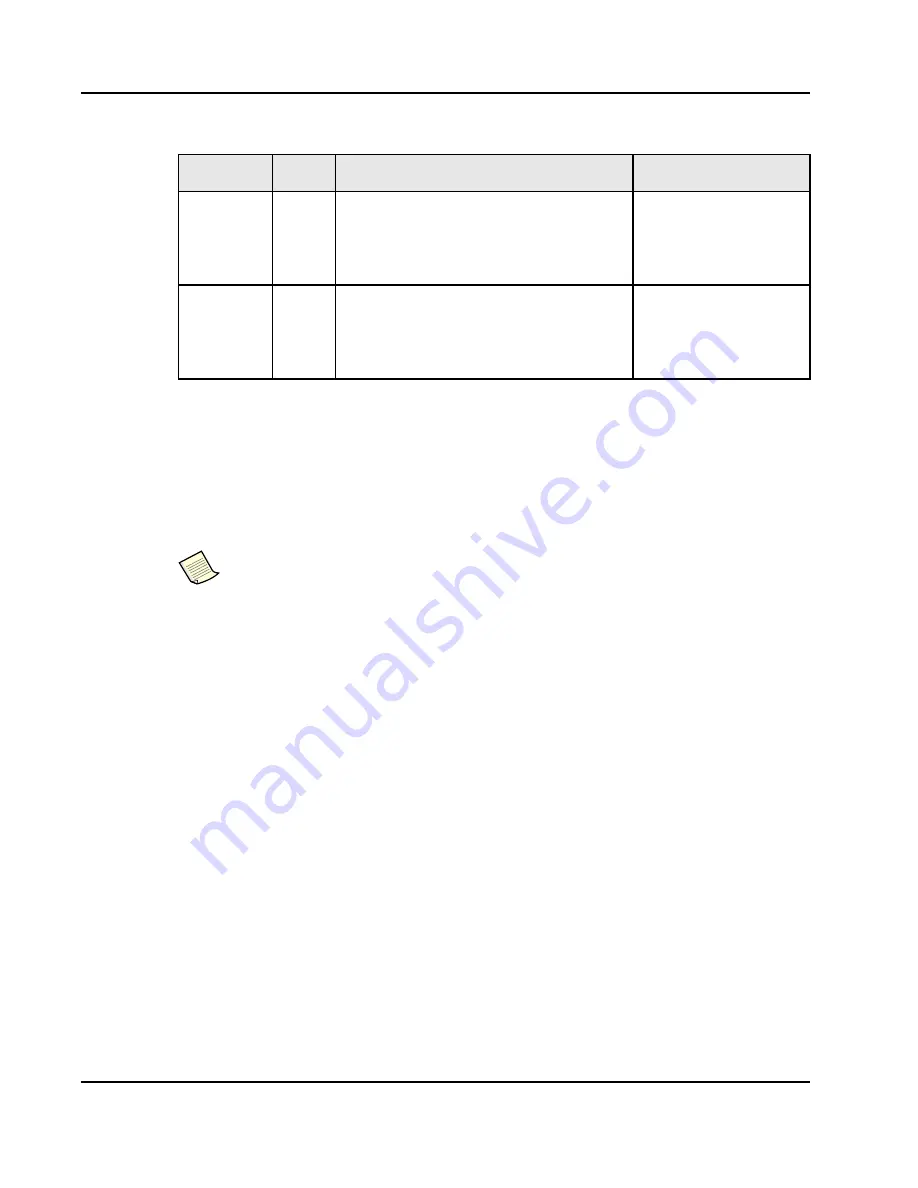

MRA

R/W

Aliases a Memory Read Command to Memory

Read Multiple Command. This causes PowerSpan

II to prefetch read data on the destination bus

(processor bus or PCI) up to the amount

programmed in the RD_AMT[2:0] field.

Disabled

RD_AMT[2:0]

R/W

Controls the prefetch read amount for a Memory

Read when MRA is enabled. Memory Read

Multiple always causes prefetch up to the value in

RD_AMT[2:0]. This can be programmed up to a

maximum of 128 bytes.

8 bytes is the default

prefetch read amount

PowerSpan II behavior is undefined if more than one overlapping target image claims a

transaction. For example, if two target image have the same base address and size, then they

must have unique master bits set in the

“PCI-1 Target Image x Translation Address Register”

Table 5: Programming Model for PCI Target Image Control Register

Bits

Type

Description

Default Setting

Содержание PowerSpan II

Страница 8: ...Contents 8 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 14: ...List of Tables 14 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 18: ...About this Document 18 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 82: ...2 PCI Interface 82 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 112: ...3 Processor Bus Interface 112 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 156: ...7 Interrupt Handling 156 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 380: ...12 Register Descriptions 380 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 394: ...14 Package Information 394 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 414: ...15 AC Timing 414 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 416: ...16 Ordering Information 416 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 420: ...A Hardware Implementation 420 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 428: ...B Typical Applications 428 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 432: ...Glossary 432 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...