2. PCI Interface

66

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

— Processor Bus I

2

O Base Address Field: Base Address of the block of IOP memory that

contains the four FIFOs (two Inbound and two Outbound). The Base Address alignment is 1

Mbyte.

— FIFO Size Field: Indicates the number of bytes required for each of the Inbound Queue and

Outbound Queue FIFOs implemented in local memory

•

I

2

O Control and Status Register (I20_ CSR)

— Host Outbound Post List Size Field: Indicates the number of entries in the Host Outbound Post

List FIFO in Host memory, used for the Outbound Option.

— I

2

O Enable Field: Enables/Disables PowerSpan II I

2

O Interface

–

PowerSpan II Primary PCI target retries I

2

O accesses until enabled

— XI

2

O Enable Field

:

Enables/Disables PowerSpan II Outbound Option

–

IPL: Inbound Post List is set when the Inbound Post list FIFO is not empty

–

OFL: Outbound Free List is set when the Outbound Free List FIFO is not empty.

•

Inbound Free List Bottom/Top/Top Increment Pointer Registers:

(IFL_BOT/IFL_TOP/IFL_TOP_INC)

— Manages the Inbound Free List circular FIFO implemented in local memory

•

Inbound Post List Bottom/Bottom Increment/Top Pointer Registers:

(IPL_BOT/IPL_BOT_INC/IPL_TOP)

— Used to manage the Inbound Post List circular FIFO implemented in local memory

•

Outbound Free List Bottom/Bottom Increment/Top Pointer Registers:

(OFL_BOT/IPL_BOT_INC/OFL_TOP)

— Used to manage the Outbound Free List circular FIFO implemented in local memory

•

Outbound Post List Bottom/Top/Top Increment Pointer Registers:

(IPL_BOT/IPL_TOP_INC/IPL_TOP)

— Used to manage the Outbound Post List circular FIFO implemented in local memory

•

IOP Outbound Index/Increment Registers: (IOP_OI/IOP_OI_INC)

— Used to manage the Host Outbound FIFO

•

Host Outbound Index/Index Alias Registers: (HOST_OI/HOST_OIA)

— Used to manage the Host Outbound FIFO

•

Host Outbound Index Offset Registers: (HOST_OIO)

— Determines offset of the I

2

O target image at which the Host Processor can access the I

2

O Host

Outbound Index Register

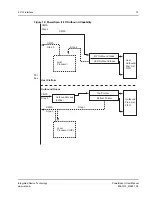

Interactions between the IOP and Host platforms during the I

2

O message passing protocols are

displayed in Figure 3.4. The solid lines indicate pointers which are maintained and incremented by the

PowerSpan II. The dashed lines indicate pointers which are incremented by the IOP. The IOP writes

one to increment to PowerSpan II increment register associated with the pointer.

Содержание PowerSpan II

Страница 8: ...Contents 8 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 14: ...List of Tables 14 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 18: ...About this Document 18 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 82: ...2 PCI Interface 82 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 112: ...3 Processor Bus Interface 112 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 156: ...7 Interrupt Handling 156 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 380: ...12 Register Descriptions 380 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 394: ...14 Package Information 394 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 414: ...15 AC Timing 414 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 416: ...16 Ordering Information 416 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 420: ...A Hardware Implementation 420 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 428: ...B Typical Applications 428 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 432: ...Glossary 432 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...