11. Signals and Pinout

192

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

11.1.2

Processor Bus Signals

This section describes PowerSpan II PB Interface signals used to interface to the 60x bus processors.

Signals in this group are 3.3V LVTTL compatible. The signals are not 5V tolerant.

summarizes the signals in this grouping. Signals with electrical characteristics different from

the remainder of the group are placed at the end of the table.

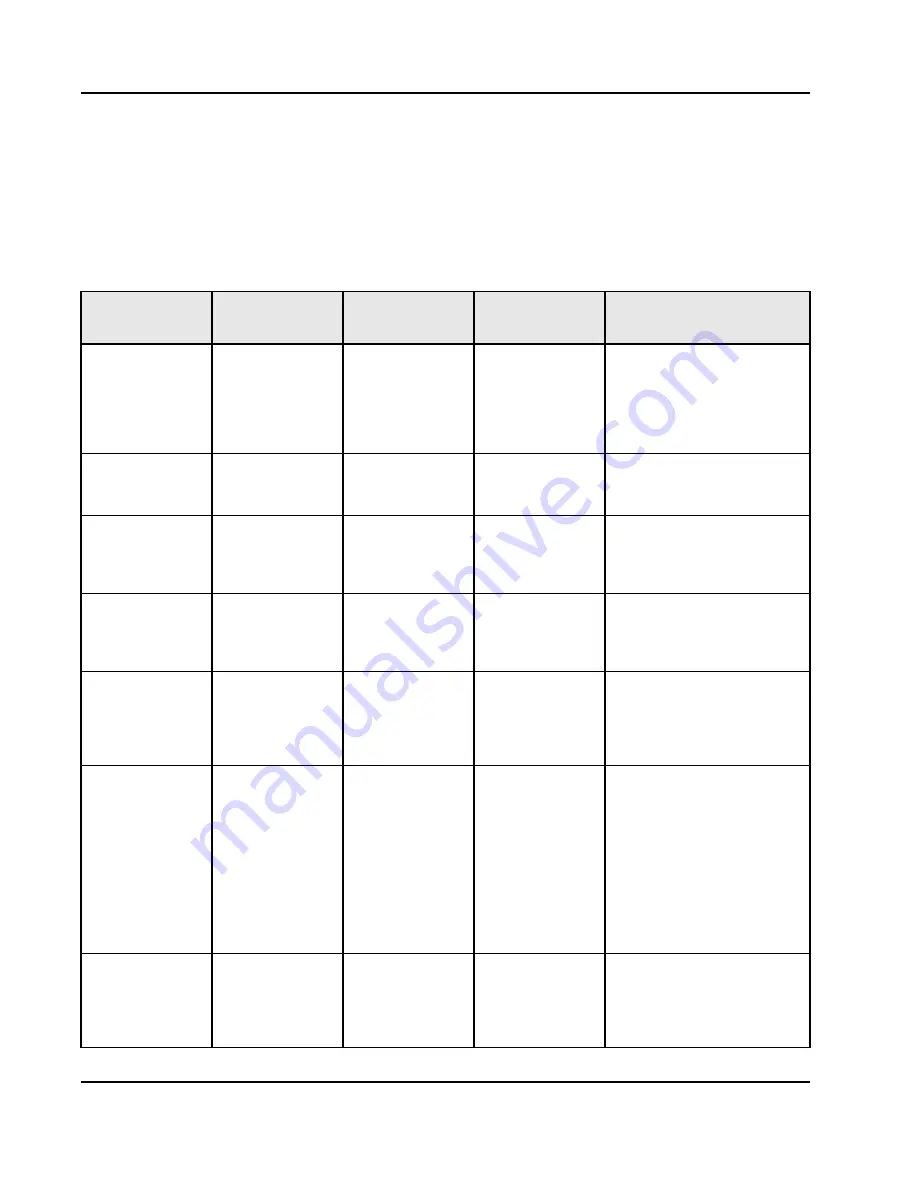

Table 55: Processor Bus Signals

Pin Name

Pin Type

Reset State

Recommended

Termination

Description

PB_AACK_

Tristate bidirectional

Hi-Z

Pull-up resistor

Address Acknowledge:

A

processor bus slave asserts this

signal to indicate that it identified

the address tenure. Assertion of

this signal terminates the address

tenure.

PB_ABB_

Tristate output

Hi-Z

Pull-up resistor

Address Bus Busy:

Indicates

ownership of the processor

address bus.

PB_AP[0:3]

Tristate bidirectional

Hi-Z

Pull-up resistor

Address Parity:

The processor

address bus master drives this

signal to indicate the parity of the

address bus.

PB_ARTRY_

Tristate bidirectional

Hi-Z

Pull-up resistor

Address Retry:

Assertion of this

signal indicates that the bus

transaction must be retried by the

processor bus master.

PB_A[0:31]

Tristate bidirectional

Hi-Z

No requirement

a

Address Bus:

Address for the

current bus cycle. It is driven by

PowerSpan II when it is the 603

bus master. At all other times it is

an input to PowerSpan II.

PB_BG[1]_

Tristate bidirectional

Hi-Z

Pull-up resistor

Address Bus Grant:

This is an

input when an external arbiter is

used and an output when the

internal arbiter is used. As input it

is used by an external arbiter to

grant the processor address bus

to PowerSpan II. As output it is

used by the internal arbiter to

grant the processor address bus

to an external bus master. This

pin must be weakly pulled high.

PB_BG[2:3]_

Tristate output

Hi-Z

Pull-up resistor

Address Bus Grant:

It is used by

the internal arbiter to grant the

processor address bus to the

external bus masters. These pins

must be weakly pulled high.

Содержание PowerSpan II

Страница 8: ...Contents 8 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 14: ...List of Tables 14 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 18: ...About this Document 18 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 82: ...2 PCI Interface 82 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 112: ...3 Processor Bus Interface 112 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 156: ...7 Interrupt Handling 156 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 380: ...12 Register Descriptions 380 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 394: ...14 Package Information 394 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 414: ...15 AC Timing 414 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 416: ...16 Ordering Information 416 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 420: ...A Hardware Implementation 420 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 428: ...B Typical Applications 428 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 432: ...Glossary 432 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...