8-4

IIC

of the halfword written, is put into the first stage and byte 1, the least significant byte of the halfword writ-

ten, is put into the second stage. In this case, byte 0, is sent out to the IIC bus first and byte 1, is sent out

second. If a byte is written when the FIFO is full, the byte is discarded; it is not put into the FIFO.

The master data buffer is used to receive data when the requested master transfer is a read. The first byte

received goes into the first stage, the second byte received goes into the second stage and so on. As data

is read out of the FIFO, any data in stage 2 is moved by the hardware into stage 1, data in stage 3 moves

into 2, etc. In the case where two bytes are read via one double-byte access, stage 1 is sent as byte 0, the

most significant byte, and stage 2 is sent to byte 1, the least significant byte. In this case, stages 3 and 4

automatically walk into stages 1 and 2. When an empty FIFO is read, whatever data was last stored in

stage 1 (stages 1 and 2 for a double-byte operation) is returned to the slave data bus.

The slave data buffer works in exactly the same way as the master data buffer with the exception that it is

used only to store data sent or received in a slave transfer on the IIC bus. This allows the overlapping of

slave and master transfer operations. The bit assignments for the master data buffer and the slave data

buffer are identical.

Care must be taken not to start a requested master operation when there is still data in the master data

buffer. If, for example, a master read transfer was requested with stale data in the buffer, then this data

would be presented to the program as data read by the requested operation.

The buffers will be flushed, set to empty, whenever the IIC interface is reset or when one of the flush bits is

set to a logic 1 in the mode control register.

8.4.2 Lo Master Address Register

When 7-bit addressing is used, only the Lo master address register needs to be written. The Hi master

address register is not used. For 7-bit addressing, bits 0:6 are used to form the address that is transmitted

on the IIC bus; bit 7 is don’t care. When 10-bit addressing is used, bits 0:7 form the second byte address

that is transmitted on the IIC bus.

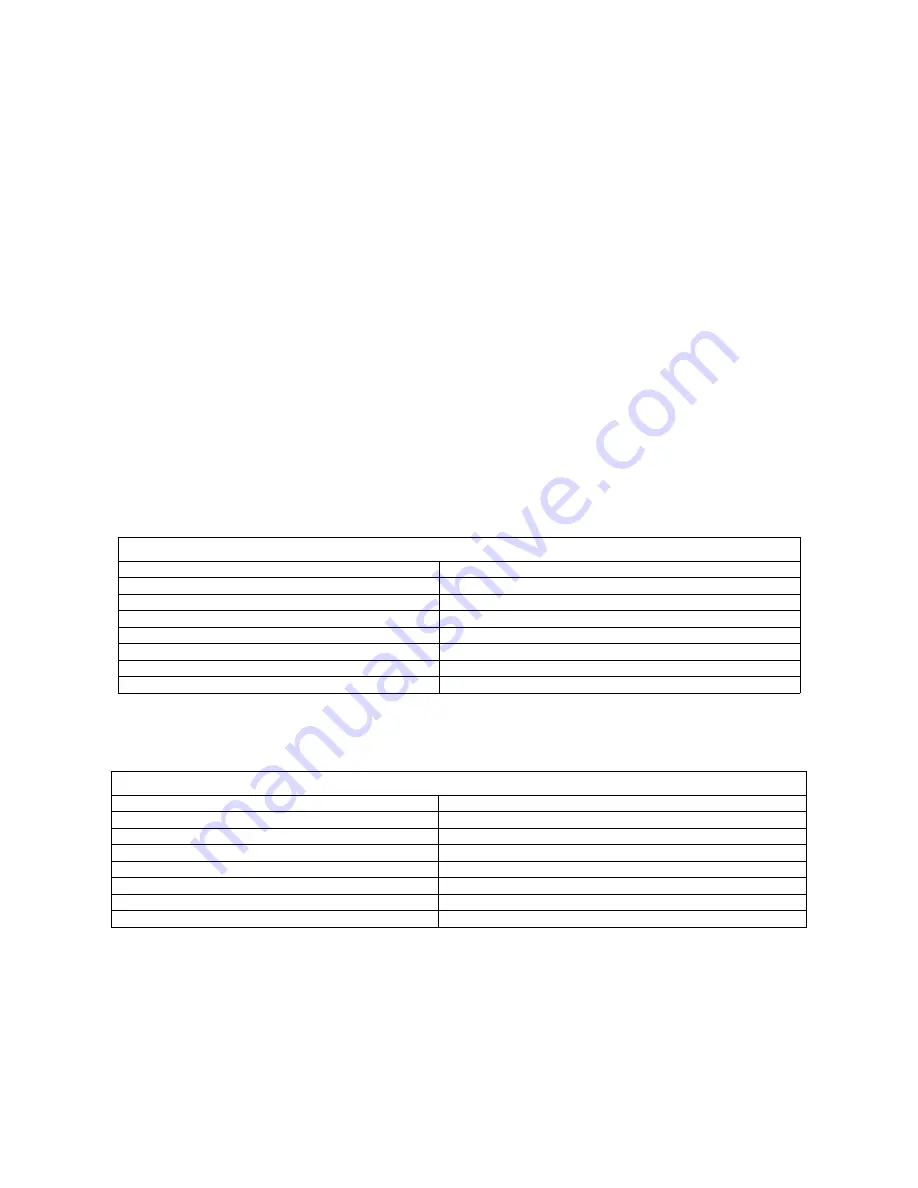

Table 79. Master Data Buffer

Address ‘FF6X_0000’ - Master Data Buffer

bit 0

Data bit 0 (MSB)

bit 1

Data bit 1

bit 2

Data bit 2

bit 3

Data bit 3

bit 4

Data bit 4

bit 5

Data bit 5

bit 6

Data bit 6

bit 7

Data bit 7 (LSB)

Table 80. Master Data Buffer

Address ‘FF6X_0002’ - Slave Data Buffer

bit 0

Data bit 0 (MSB)

bit 1

Data bit 1

bit 2

Data bit 2

bit 3

Data bit 3

bit 4

Data bit 4

bit 5

Data bit 5

bit 6

Data bit 6

bit 7

Data bit 7 (LSB)

Содержание CPC700

Страница 1: ...CPC700 Memory Controller and PCI Bridge User s Manual Version 1 1 Issue Date 3 22 00 Preliminary...

Страница 10: ...Table of Contents x Table of Contents...

Страница 16: ...Tables xvi List of Tables...

Страница 28: ...1 12 CPC700 User s Manual Preliminary...

Страница 72: ...3 36 Processor Interface...

Страница 132: ...4 60 Memory Controller...

Страница 184: ...5 52 PCI Interface...

Страница 194: ...6 10 Clock Power Management and Reset...

Страница 224: ...8 18 IIC...

Страница 244: ...10 10 Interrupt Controller...

Страница 246: ...I 11 2 JTAG...

Страница 250: ...12 4 Processor Local Bus PLB...

Страница 262: ...14 10 Register Summary...

Страница 267: ...CPC700 User s Manual Preliminary...