250

CHAPTER 16 8/16-BIT COMPOSITE TIMER

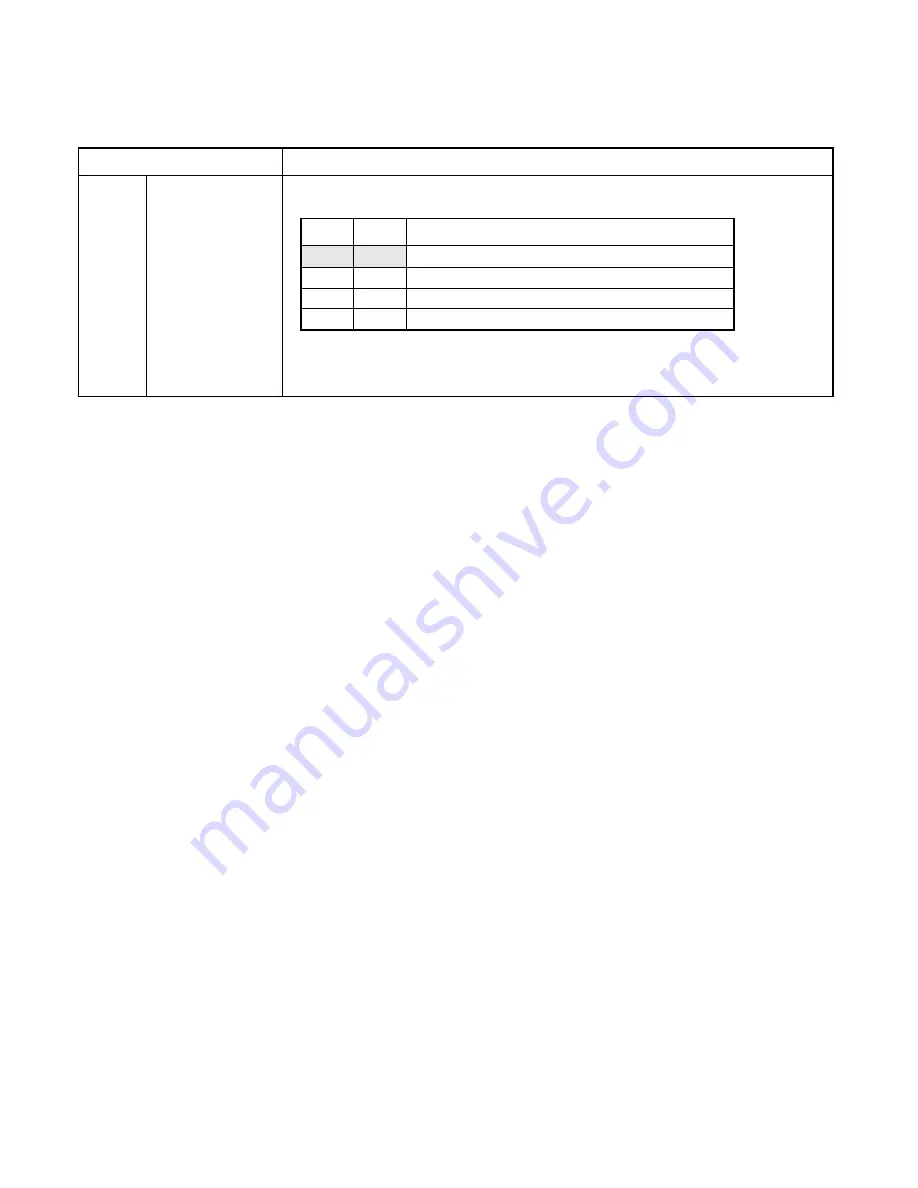

bit1

bit0

FE01, FE00:

Timer 00 filter function

select bits

These bits select the filter function for the external signal (EC00) to timer 00 when the PWC timer

or input capture function has been selected.

• An attempt to write to these bits is nullified during timer operation (T00CR1:STA = 1).

• The settings of these bits have no effect on operation when the interval timer or PWM timer

function has been selected (filter function does not operate.).

Table 16.5-3 Functional Description of Each Bit of 8/16-bit Composite Timer 00/01 Timer Mode Control

Register (TMCR0) (2 / 2)

Bit name

Function

FE01

FE00

Timer 00 filter function select bits

0

0

No filtering

0

1

Removing H pulse noise

1

0

Removing L pulse noise

1

1

Removing H/L pulse noise

Содержание F2 MC-8FX Family

Страница 2: ......

Страница 4: ......

Страница 30: ...16 CHAPTER 1 DESCRIPTION 1 FPT 64P M23 FPT 64P M24 2 For the I O circuit type refer to 1 8 I O Circuit Type ...

Страница 34: ...20 CHAPTER 1 DESCRIPTION ...

Страница 35: ...21 CHAPTER 2 HANDLING DEVICES This chapter gives notes on using 2 1 Device Handling Precautions ...

Страница 38: ...24 CHAPTER 2 HANDLING DEVICES ...

Страница 39: ...25 CHAPTER 3 MEMORY SPACE This chapter describes memory space 3 1 Memory Space 3 2 Memory Map ...

Страница 43: ...29 CHAPTER 4 MEMORY ACCESS MODE This chapter describes the memory access mode 4 1 Memory Access Mode ...

Страница 56: ...42 CHAPTER 5 CPU ...

Страница 73: ...59 CHAPTER 6 CLOCK CONTROLLER ...

Страница 96: ...82 CHAPTER 6 CLOCK CONTROLLER ...

Страница 104: ...90 CHAPTER 7 RESET ...

Страница 105: ...91 CHAPTER 8 INTERRUPTS This chapter explains the interrupts 8 1 Interrupts ...

Страница 174: ...160 CHAPTER 10 TIMEBASE TIMER ...

Страница 184: ...170 CHAPTER 10 TIMEBASE TIMER ...

Страница 218: ...204 CHAPTER 13 WATCH PRESCALER ...

Страница 257: ...243 CHAPTER 16 8 16 BIT COMPOSITE TIMER ...

Страница 261: ...247 CHAPTER 16 8 16 BIT COMPOSITE TIMER ...

Страница 288: ...274 CHAPTER 16 8 16 BIT COMPOSITE TIMER ...

Страница 301: ...287 CHAPTER 17 16 BIT PPG TIMER ...

Страница 316: ...302 CHAPTER 17 16 BIT PPG TIMER ...

Страница 382: ...368 CHAPTER 21 UART SIO DEDICATED BAUD RATE GENERATOR ...

Страница 390: ...376 CHAPTER 22 I2C ...

Страница 395: ...381 CHAPTER 22 I2C ...

Страница 399: ...385 CHAPTER 22 I2C ...

Страница 430: ...416 CHAPTER 23 10 BIT A D CONVERTER ...

Страница 476: ...462 CHAPTER 24 LCD CONTROLLER ...

Страница 482: ...468 CHAPTER 25 LOW VOLTAGE DETECTION RESET CIRCUIT ...

Страница 494: ...480 CHAPTER 26 CLOCK SUPERVISOR ...

Страница 507: ...493 CHAPTER 27 REAL TIME CLOCK ...

Страница 523: ...509 CHAPTER 27 REAL TIME CLOCK ...

Страница 532: ...518 CHAPTER 27 REAL TIME CLOCK ...

Страница 536: ...522 CHAPTER 28 256 KBIT FLASH MEMORY ...

Страница 554: ...540 CHAPTER 28 256 KBIT FLASH MEMORY ...

Страница 564: ...550 CHAPTER 29 EXAMPLE OF SERIAL PROGRAMMING CONNECTION ...

Страница 595: ...581 INDEX INDEX The index follows on the next page This is listed in alphabetic order ...

Страница 596: ...582 INDEX Index ...

Страница 597: ...583 INDEX ...

Страница 599: ...585 Pin Function Index V2 LCD power supply driving pin 2 439 V3 LCD power supply driving pin 3 439 ...

Страница 600: ...586 Pin Function Index ...

Страница 602: ......