399

CHAPTER 22 I

2

C

■

General Call Address

A general call address consists of the start address byte (00

H

) and the second address byte that follows. To

use a general call address, you must set IBCR10:GACKE=1 before the acknowledge of the first byte

general call address. Also, the acknowledgment for the second address byte can be controlled as shown

below.

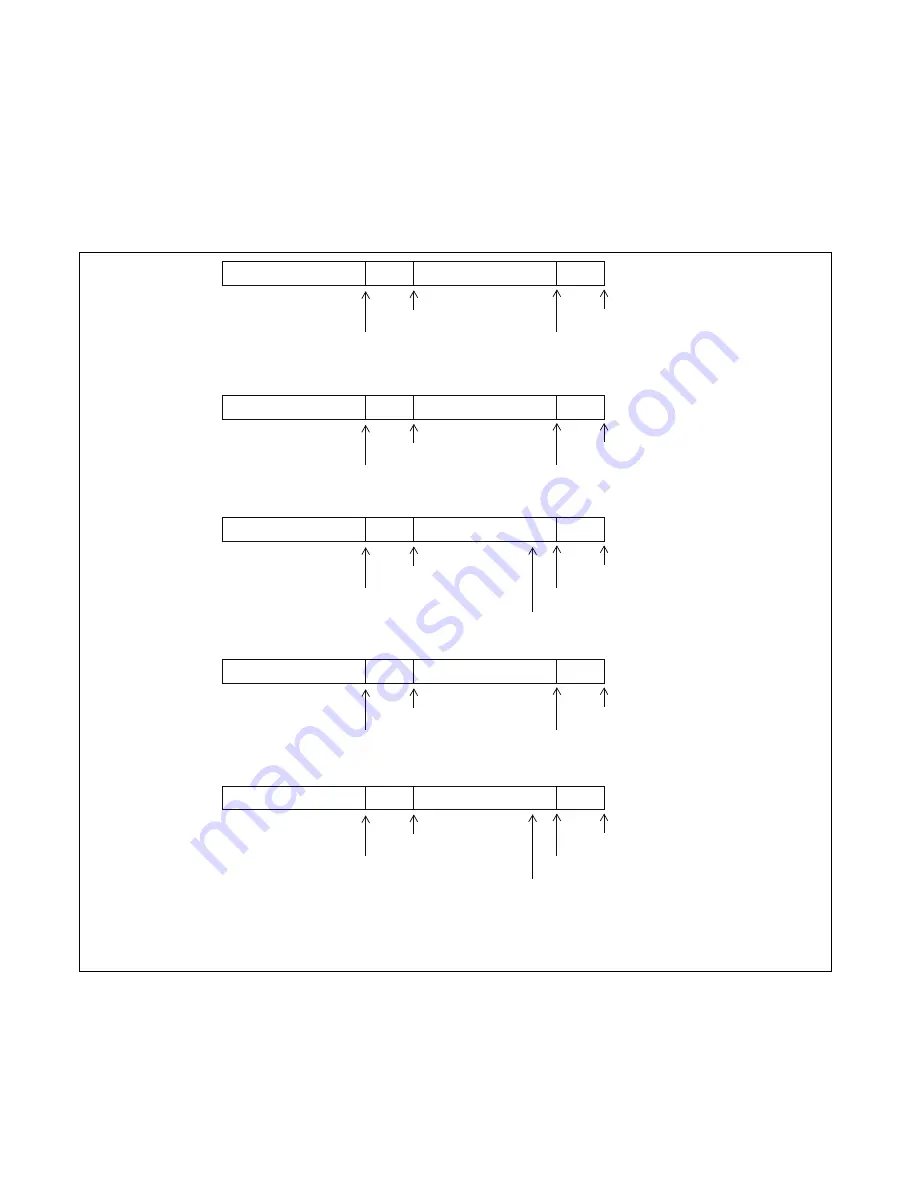

Figure 22.7-2 General Call Operation

If this module sends a general call address at the same time as another device, you can determine whether

the module successfully seized control of the bus by checking whether arbitration lost was detected when

the second address byte was transferred. If arbitration lost was detected, the module goes to slave mode and

continues to receive data from the master.

First-byte general call address

Second-byte general call address

ACK

ACK/NACK

Slave mode

(a) General call operation in slave mode

Master mode

(b) General call operation in master mode (Start from GACKE = 1 with no AL.)

Master mode

(c) General call operation in master mode (Start from GACKE = 1 with AL generated by second address.)

Master mode

(d) General call operation in master mode (Start from GACKE = 0 with no AL.)

Master mode

(e) General call operation in master mode (Start from GACKE = 0 with AL generated by second address.)

GACKE=1

GACKE=1

GACKE=0

GACKE=0

ACK :

Acknowledgment

NACK : No acknowledgment

GCA : General call address

AL

: Arbitration lost

When IBCR10:GACKE = 1,

ACK is given and IBSR0:GCA is set.

IBCR10:INT is set at 9th SCL

↓

.

Set IBCR00:INTS = 1.

IBCR10:INT is set at 9th SCL

↓

.

Read IBSR0: LRB.

IBCR10:INT is set at 8th SCL

↓

.

Read IDDR0 and control ACK/NACK by IBCR10:DACKE.

To read IBSR10:LRB, set INTS = 0.

IBCR10:INT is set at 8th SCL

↓

.

Read IDDR0 and control ACK/NACK by IBCR10:DACKE.

To read IBSR10:LRB, set INTS = 0.

ACK is given and IBSR0:GCA is set.

ACK is given and IBSR0:GCA is set.

IBCR10:INT is set at 9th SCL

↓

.

Set IBCR00:INTS = 1 and GACKE = 0.

IBCR10:INT is set at 9th SCL

↓

.

Set IBCR00:INTS = 1 and GACKE = 0.

IBCR10:INT is set at 9th SCL

↓

.

Read IBSR0:LRB.

IBCR10:INT is set at 9th SCL

↓

.

Read IBSR0:LRB.

IBCR10:INT is set at 8th SCL

↓

.

Read IDDR0 and control ACK/NACK by IBCR10:DACKE.

To read IBSRl:LRB, set INT S = 0.

IBCR10:INT is set at 9th SCL

↓

.

Read IBSR0:LRB.

IBCR10:INT is set at 9th SCL

↓

.

Read IBSR0:LRB.

IBCR10:INT is set at 8th SCL

↓

.

Set INTS = 0 to read IBSR10:LRB.

AL is generated by second address and switches to slave mode.

IBCR10:INT is set at 9th SCL

↓

.

Set IBCR00:INTS = 1.

ACK is not given and IBSR0:GCA is not set.

IBCR10:INT is set at 9th SCL

↓

.

Set IBCR00:INTS = 1.

ACK is not given and IBSR0:GCA is not set.

AL is generated by second address, IBSR0:GCA is set,

and switches to slave mode.

IBCR10:INT is set at 8th SCL

↓

.

To read IBSR10:LRB, set INTS = 0.

GCA is cleared.

First-byte general call address

Second-byte general call address

ACK

ACK/NACK

First-byte general call address

Second-byte general call address

ACK

ACK/NACK

First-byte general call address

Second-byte general call address

ACK

ACK/NACK

First-byte general call address

Second-byte general call address

ACK

ACK/NACK

Содержание F2 MC-8FX Family

Страница 2: ......

Страница 4: ......

Страница 30: ...16 CHAPTER 1 DESCRIPTION 1 FPT 64P M23 FPT 64P M24 2 For the I O circuit type refer to 1 8 I O Circuit Type ...

Страница 34: ...20 CHAPTER 1 DESCRIPTION ...

Страница 35: ...21 CHAPTER 2 HANDLING DEVICES This chapter gives notes on using 2 1 Device Handling Precautions ...

Страница 38: ...24 CHAPTER 2 HANDLING DEVICES ...

Страница 39: ...25 CHAPTER 3 MEMORY SPACE This chapter describes memory space 3 1 Memory Space 3 2 Memory Map ...

Страница 43: ...29 CHAPTER 4 MEMORY ACCESS MODE This chapter describes the memory access mode 4 1 Memory Access Mode ...

Страница 56: ...42 CHAPTER 5 CPU ...

Страница 73: ...59 CHAPTER 6 CLOCK CONTROLLER ...

Страница 96: ...82 CHAPTER 6 CLOCK CONTROLLER ...

Страница 104: ...90 CHAPTER 7 RESET ...

Страница 105: ...91 CHAPTER 8 INTERRUPTS This chapter explains the interrupts 8 1 Interrupts ...

Страница 174: ...160 CHAPTER 10 TIMEBASE TIMER ...

Страница 184: ...170 CHAPTER 10 TIMEBASE TIMER ...

Страница 218: ...204 CHAPTER 13 WATCH PRESCALER ...

Страница 257: ...243 CHAPTER 16 8 16 BIT COMPOSITE TIMER ...

Страница 261: ...247 CHAPTER 16 8 16 BIT COMPOSITE TIMER ...

Страница 288: ...274 CHAPTER 16 8 16 BIT COMPOSITE TIMER ...

Страница 301: ...287 CHAPTER 17 16 BIT PPG TIMER ...

Страница 316: ...302 CHAPTER 17 16 BIT PPG TIMER ...

Страница 382: ...368 CHAPTER 21 UART SIO DEDICATED BAUD RATE GENERATOR ...

Страница 390: ...376 CHAPTER 22 I2C ...

Страница 395: ...381 CHAPTER 22 I2C ...

Страница 399: ...385 CHAPTER 22 I2C ...

Страница 430: ...416 CHAPTER 23 10 BIT A D CONVERTER ...

Страница 476: ...462 CHAPTER 24 LCD CONTROLLER ...

Страница 482: ...468 CHAPTER 25 LOW VOLTAGE DETECTION RESET CIRCUIT ...

Страница 494: ...480 CHAPTER 26 CLOCK SUPERVISOR ...

Страница 507: ...493 CHAPTER 27 REAL TIME CLOCK ...

Страница 523: ...509 CHAPTER 27 REAL TIME CLOCK ...

Страница 532: ...518 CHAPTER 27 REAL TIME CLOCK ...

Страница 536: ...522 CHAPTER 28 256 KBIT FLASH MEMORY ...

Страница 554: ...540 CHAPTER 28 256 KBIT FLASH MEMORY ...

Страница 564: ...550 CHAPTER 29 EXAMPLE OF SERIAL PROGRAMMING CONNECTION ...

Страница 595: ...581 INDEX INDEX The index follows on the next page This is listed in alphabetic order ...

Страница 596: ...582 INDEX Index ...

Страница 597: ...583 INDEX ...

Страница 599: ...585 Pin Function Index V2 LCD power supply driving pin 2 439 V3 LCD power supply driving pin 3 439 ...

Страница 600: ...586 Pin Function Index ...

Страница 602: ......