383

CHAPTER 22 I

2

C

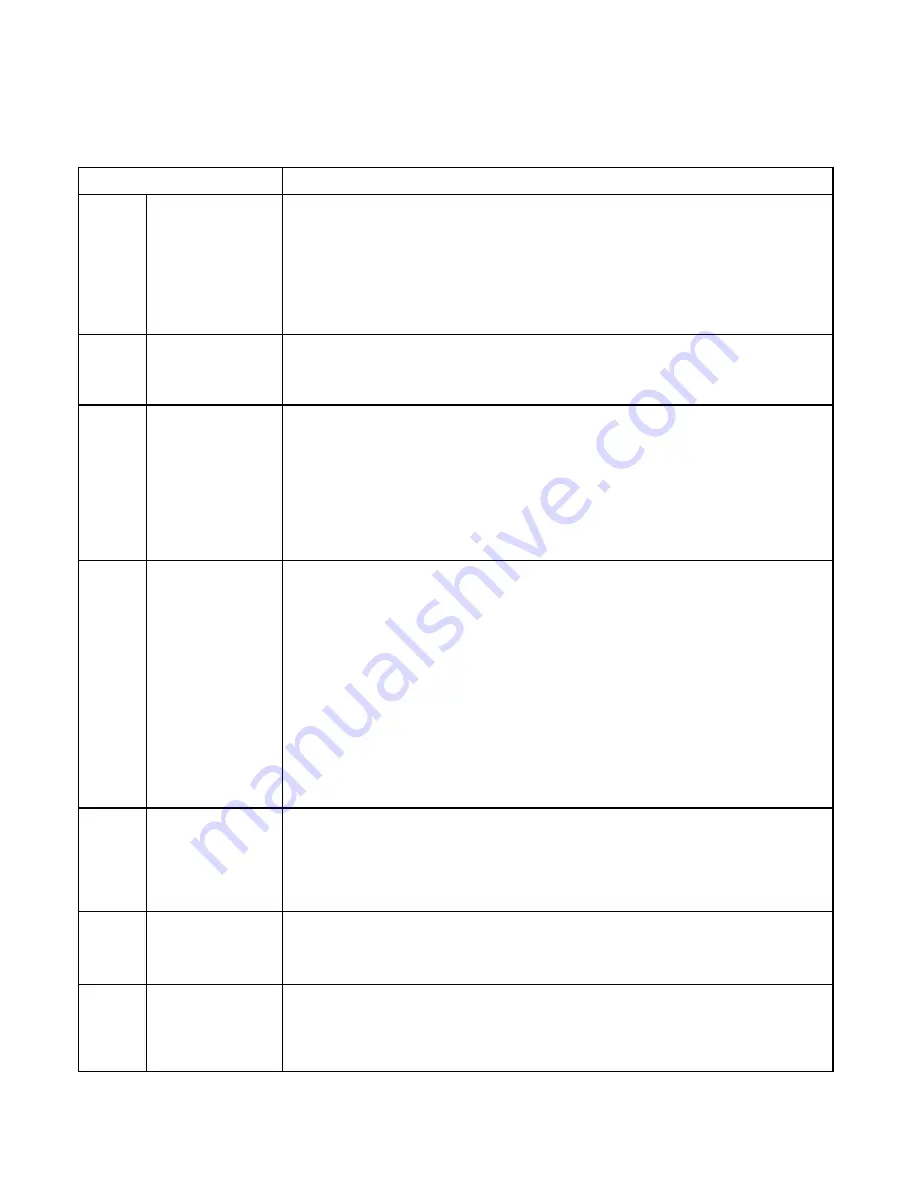

Table 22.5-2 I

2

C Bus Control Register 1 (IBCR10) (1 / 2)

Bit name

Function

bit7

BER:

Bus error interrupt

request flag bit

This bit is used to detect bus errors.

• A bus error interrupt request is generated if this bit and the IBCR10:BEIE bit are both "1".

• This bit is set to "1" when an invalid start or stop condition is detected.

Setting the bit to "0": Clears itself (changes the value to "0").

Setting the bit to "1": Leaves its value unchanged without affecting the operation.

• The bit returns "1" when read by a read-modify-write operation.

• When this bit is set to "1", ICCR0:EN is set to "0", and the I

2

C interface enters halt mode to

terminate data transfer.

bit6

BEIE:

Bus error interrupt

request enable bit

This bit enables or disables bus error interrupts.

• A bus error interrupt request is generated if this bit and the IBCR10:BER bit are both "1".

Setting the bit to "0": Disables bus error interrupts.

Setting the bit to "1": Enables bus error interrupts.

bit5

SCC:

Start condition

generation bit

This bit can be used to generate a start condition repeatedly to restart communications in master

mode.

• Writing "1" to the bit in master mode generates a start condition repeatedly.

• Writing "0" to the bit is meaningless.

• When read, the bit returns "0".

Note:

• Do not set IBCR10:SCC = 1 and IBCR10:MSS = 0 at the same time.

• An attempt to write "1" to this bit is ignored when IBCR10:INT = 0 (no start condition is

generated). If you write "1" to this bit and "0" to the IBCR10:INT bit at the same time

when the IBCR10:INT = 1, this bit takes priority and generates a start condition.

bit4

MSS:

Master/slave select bit

This bit selects master mode or slave mode.

• Writing "1" to this bit while the I

2

C bus is in the idle state (IBSR0:BB = 0) selects master mode,

generates a start condition, and then starts address transfer.

• Writing "0" to the bit while the I

2

C bus is in the busy state (IBSR0:BB = 1) selects slave mode,

generates a stop condition, and then ends data transfer.

• If arbitration lost occurs during data or address transfer in master mode, this bit is cleared to "0"

and the mode changes to slave mode.

Note:

• Do not set IBCR10:SCC = 1 and IBCR10:MSS = 0 at the same time.

• An attempt to write "0" to this bit is ignored when IBCR10:INT = 0. If you write "0" to

this bit and "0" to the IBCR10:INT bit at the same time when the IBCR10:INT = 1, this

bit takes priority and generates a stop condition.

• The IBCR00:ALF bit is not set even though you write "1" to the MSS bit during

transmission or reception in slave mode. Do not write "1" to the MSS bit during

transmission or reception in slave mode.

bit3

DACKE:

Data acknowledge

enable bit

This bit controls data acknowledgment during data reception.

Setting the bit to "0": Disables data acknowledge output.

Setting the bit to "1": Enables data acknowledge output. In this case, data acknowledgment is

output in the ninth SCL0 cycle during data reception in master mode. In

slave mode, data acknowledgment is output in the ninth SCL0 cycle only if

address acknowledgment has already been output.

bit2

GACKE:

General call address

acknowledge enable bit

This bit controls general call address acknowledgment.

Setting the bit to "0": Disables output of general call address acknowledge.

Setting the bit to "1": Causes a general call address acknowledgment to be output if a general call

address (00

H

) is received in master or slave mode.

bit1

INTE:

Transfer completion

interrupt enable bit

This bit enables or disables transfer completion interrupts.

Setting the bit to "0": Disables transfer completion interrupts.

Setting the bit to "1": Enables transfer completion interrupts.

• A transfer completion interrupt request is generated if this bit and the IBCR10:INT bit are both

"1".

Содержание F2 MC-8FX Family

Страница 2: ......

Страница 4: ......

Страница 30: ...16 CHAPTER 1 DESCRIPTION 1 FPT 64P M23 FPT 64P M24 2 For the I O circuit type refer to 1 8 I O Circuit Type ...

Страница 34: ...20 CHAPTER 1 DESCRIPTION ...

Страница 35: ...21 CHAPTER 2 HANDLING DEVICES This chapter gives notes on using 2 1 Device Handling Precautions ...

Страница 38: ...24 CHAPTER 2 HANDLING DEVICES ...

Страница 39: ...25 CHAPTER 3 MEMORY SPACE This chapter describes memory space 3 1 Memory Space 3 2 Memory Map ...

Страница 43: ...29 CHAPTER 4 MEMORY ACCESS MODE This chapter describes the memory access mode 4 1 Memory Access Mode ...

Страница 56: ...42 CHAPTER 5 CPU ...

Страница 73: ...59 CHAPTER 6 CLOCK CONTROLLER ...

Страница 96: ...82 CHAPTER 6 CLOCK CONTROLLER ...

Страница 104: ...90 CHAPTER 7 RESET ...

Страница 105: ...91 CHAPTER 8 INTERRUPTS This chapter explains the interrupts 8 1 Interrupts ...

Страница 174: ...160 CHAPTER 10 TIMEBASE TIMER ...

Страница 184: ...170 CHAPTER 10 TIMEBASE TIMER ...

Страница 218: ...204 CHAPTER 13 WATCH PRESCALER ...

Страница 257: ...243 CHAPTER 16 8 16 BIT COMPOSITE TIMER ...

Страница 261: ...247 CHAPTER 16 8 16 BIT COMPOSITE TIMER ...

Страница 288: ...274 CHAPTER 16 8 16 BIT COMPOSITE TIMER ...

Страница 301: ...287 CHAPTER 17 16 BIT PPG TIMER ...

Страница 316: ...302 CHAPTER 17 16 BIT PPG TIMER ...

Страница 382: ...368 CHAPTER 21 UART SIO DEDICATED BAUD RATE GENERATOR ...

Страница 390: ...376 CHAPTER 22 I2C ...

Страница 395: ...381 CHAPTER 22 I2C ...

Страница 399: ...385 CHAPTER 22 I2C ...

Страница 430: ...416 CHAPTER 23 10 BIT A D CONVERTER ...

Страница 476: ...462 CHAPTER 24 LCD CONTROLLER ...

Страница 482: ...468 CHAPTER 25 LOW VOLTAGE DETECTION RESET CIRCUIT ...

Страница 494: ...480 CHAPTER 26 CLOCK SUPERVISOR ...

Страница 507: ...493 CHAPTER 27 REAL TIME CLOCK ...

Страница 523: ...509 CHAPTER 27 REAL TIME CLOCK ...

Страница 532: ...518 CHAPTER 27 REAL TIME CLOCK ...

Страница 536: ...522 CHAPTER 28 256 KBIT FLASH MEMORY ...

Страница 554: ...540 CHAPTER 28 256 KBIT FLASH MEMORY ...

Страница 564: ...550 CHAPTER 29 EXAMPLE OF SERIAL PROGRAMMING CONNECTION ...

Страница 595: ...581 INDEX INDEX The index follows on the next page This is listed in alphabetic order ...

Страница 596: ...582 INDEX Index ...

Страница 597: ...583 INDEX ...

Страница 599: ...585 Pin Function Index V2 LCD power supply driving pin 2 439 V3 LCD power supply driving pin 3 439 ...

Страница 600: ...586 Pin Function Index ...

Страница 602: ......