Basics communication

EL5101, EL5101-0010, EL5101-0011

31

Version: 4.2

• A right-shift (positive shift value) will delay the counter value query, which means the position value

becomes more current from the PLC perspective. However, this increases the risk that the position

determination may not be finished in time before the arrival of EtherCAT frame, so that no current

position value is available in this cycle.

• A left-shift (negative shift value) means the counter value will be queried earlier, resulting in older

position values, with an associated increase in the safety buffer before the arrival of the EtherCAT

datagram. This setting may be useful in systems with high real-time jitter, if no Industrial PCs from

Beckhoff are used for control purposes, for example.

Attention

Attention! Risk of device damage!

The mentioned notes and information should be used advisedly. The EtherCAT master au-

tomatically allocates SYNC0 and SYNC1 settings that support reliable and timely process

data acquisition. User intervention at this point may lead to undesired behavior. If these set-

tings are changed in the System Manager, no plausibility checks are carried out on the soft-

ware side. Correct function of the terminal with all conceivable setting options cannot be

guaranteed.

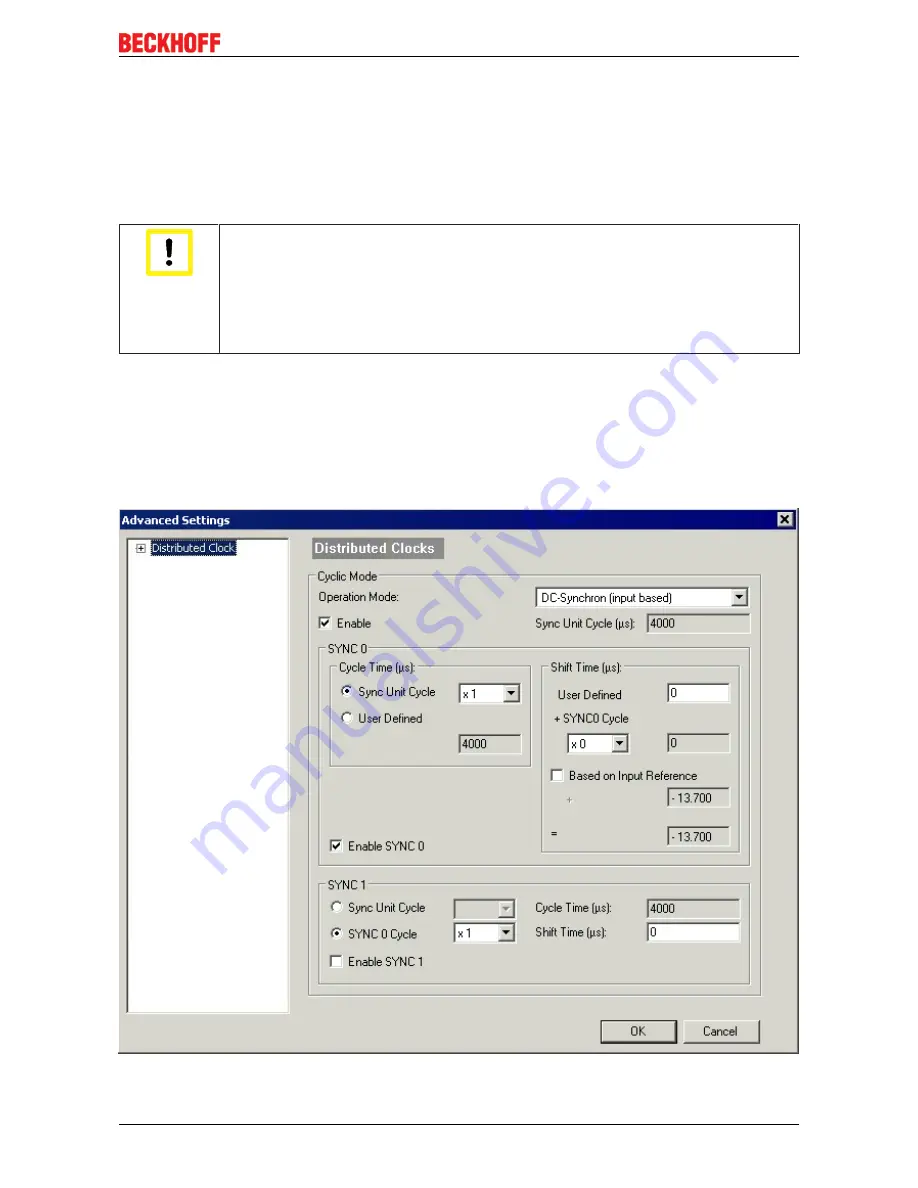

Default setting

The cyclic read of the inputs is triggered by the SYNC0 pulse (interrupt) from the DC in the EL51xx. The

EtherCAT master sets the Sync Unit Cycle time value to the PLC cycle time and therefore the EtherCAT

cycle time as standard. See Fig.

Advanced Distributed Clock (DC) settings, EL51xx terminal:

4000µs = 4 ms,

as TwinCAT is in configuration mode.

EL51xx DC settings

Fig. 20: Advanced Distributed Clock (DC) settings, EL51xx terminal