Bus Interface Unit and Write Buffer

6-4

Copyright © ARM Limited 2000. All rights reserved.

6.2.3

Burst sizes

The ARM946E-S supports the burst types listed in Table 6-1.

Incrementing bursts have an address increment of four (that is, word increment).

6.2.4

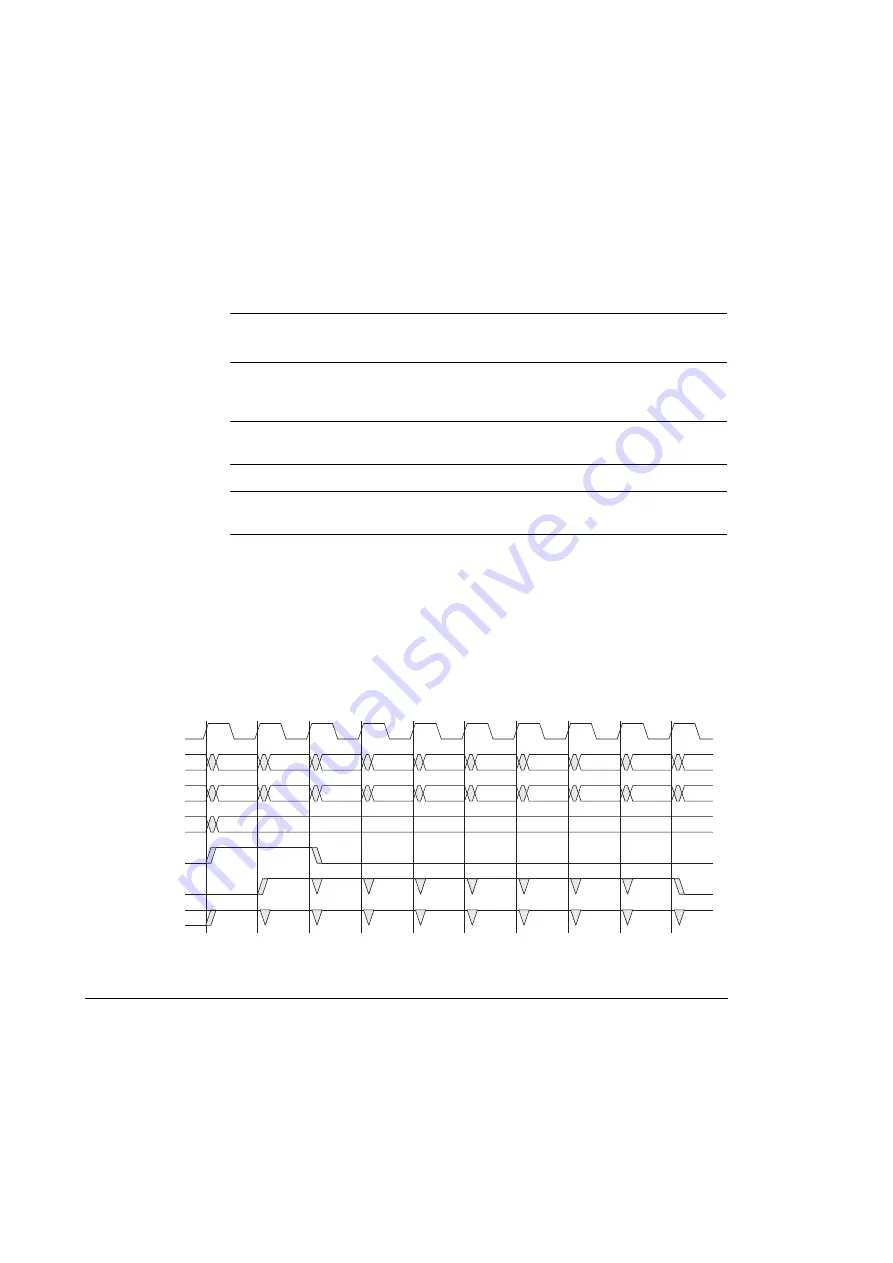

Linefetch transfers

The ARM946E-S is optimized to run with both the ICache and DCache enabled. If a

memory request (either instruction or data) to a cachable area misses in the cache the

ARM946E-S performs a linefetch.

A linefetch transfer is shown in Figure 6-1.

Figure 6-1 Linefetch transfer

Table 6-1 Supported burst types

Burst type

HBURST

encoding

Use

SINGLE

000

Single writes (

STR

/

STRH

/

STRB

)

Uncached single reads

Uncached instruction fetches

INCR

001

Store multiple (

STM

)

Uncached burst reads (

LDM

)

INCR4

011

Dirty half-cache line write back

INCR8

101

Dirty cache line write back

Cache linefetches

CLK

HTRANS

HADDR

HBURST

HBUSREQ

HGRANT

HREADY

NSEQ

NSEQ

NSEQ

SEQ

SEQ

SEQ

SEQ

SEQ

SEQ

SEQ

A

A

A

A+0x04

A+0x08

A+0xC

A+0x10

A+0x14

A+0x18

A+0x1C

INCR8

Содержание ARM946E-S

Страница 1: ...ARM DDI 0155A ARM946E S Technical Reference Manual ...

Страница 6: ...vi Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A 04 Limited Confidential ...

Страница 54: ...Programmer s Model 2 34 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 70: ...Caches 3 16 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 78: ...Protection Unit 4 8 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 98: ...Bus Interface Unit and Write Buffer 6 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 112: ...Coprocessor Interface 7 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...