Debug Support

8-22

Copyright © ARM Limited 2000. All rights reserved.

entry to debug state, in ARM state, the instruction

SUB PC, PC, #20

is scanned in and

the processor restarted, execution flow returns to the next instruction in the code

sequence.

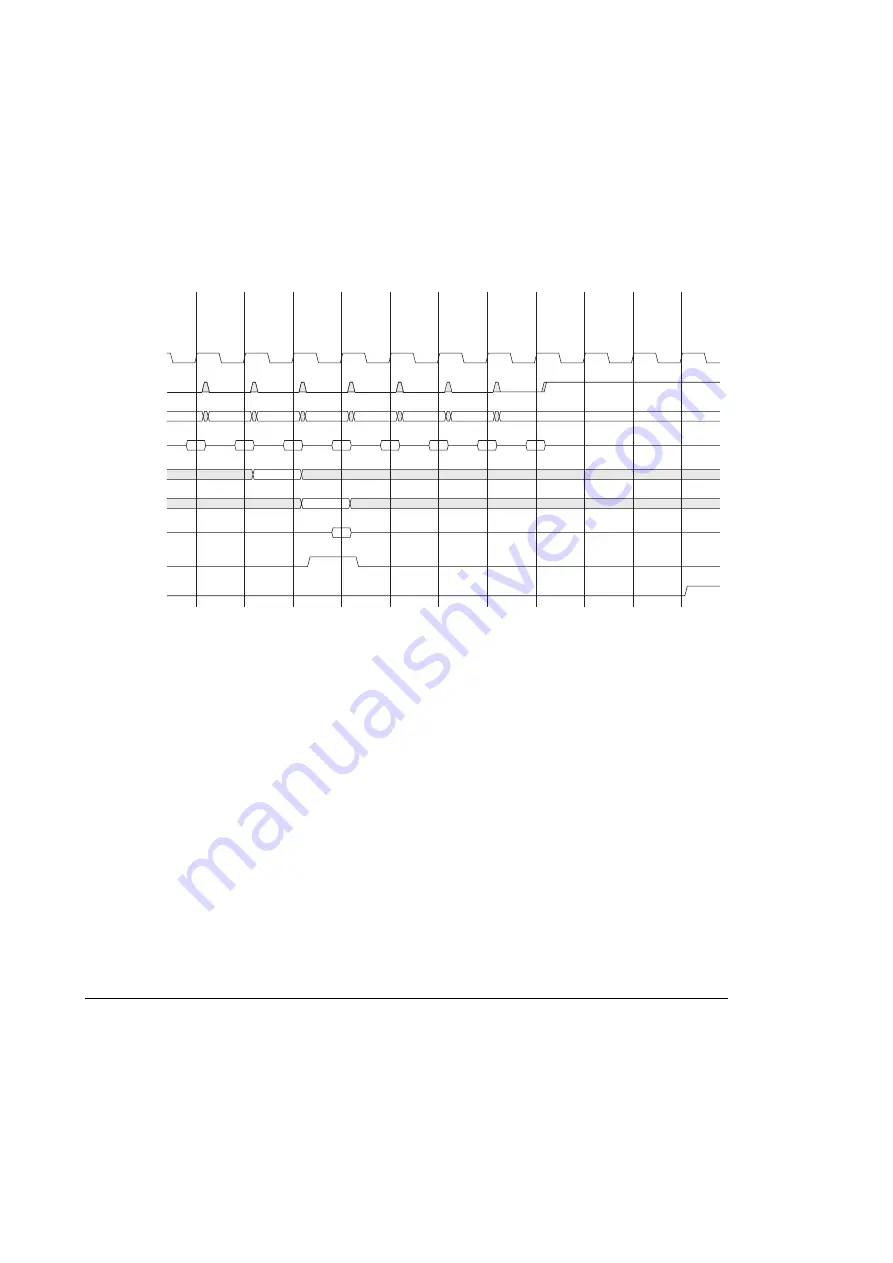

Figure 8-9 Watchpoint entry with branch

8.6.4

Watchpoints and exceptions

If a watchpointed data access is also abort, the watchpoint condition is registered and

the exception entry sequence performed. Then the processor enters debug state. If there

is an interrupt pending, the ARM9E-S allows the exception entry sequence to occur and

then enters debug state.

8.6.5

Debug request

A debug request can take place through the EmbeddedICE-RT logic or by asserting the

EDBGRQ signal. The request is synchronized and passed to the processor. Debug

request takes priority over any pending interrupt. Following synchronization, the core

enters debug state when the instruction at the execution stage of the pipeline has

CLK

INSTR[31:0]

InMREQ

RDATA[31:0]

LDR

WDATA[31:0]

DA[31:0]

B

X

X

T

T+4

Mldr

Eldr

Wldr

Dldr

Fldr

MB

EB

WB

DB

FB

ET

DT

FT

Edebug1

Ddebug

Edebug2

T+8

T+C

DBGDEWPT

DBGACK

IA[31:1]

Содержание ARM946E-S

Страница 1: ...ARM DDI 0155A ARM946E S Technical Reference Manual ...

Страница 6: ...vi Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A 04 Limited Confidential ...

Страница 54: ...Programmer s Model 2 34 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 70: ...Caches 3 16 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 78: ...Protection Unit 4 8 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 98: ...Bus Interface Unit and Write Buffer 6 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 112: ...Coprocessor Interface 7 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...