Instruction manual

–

AQ F3x0 Feeder protection IED

78 (162

)

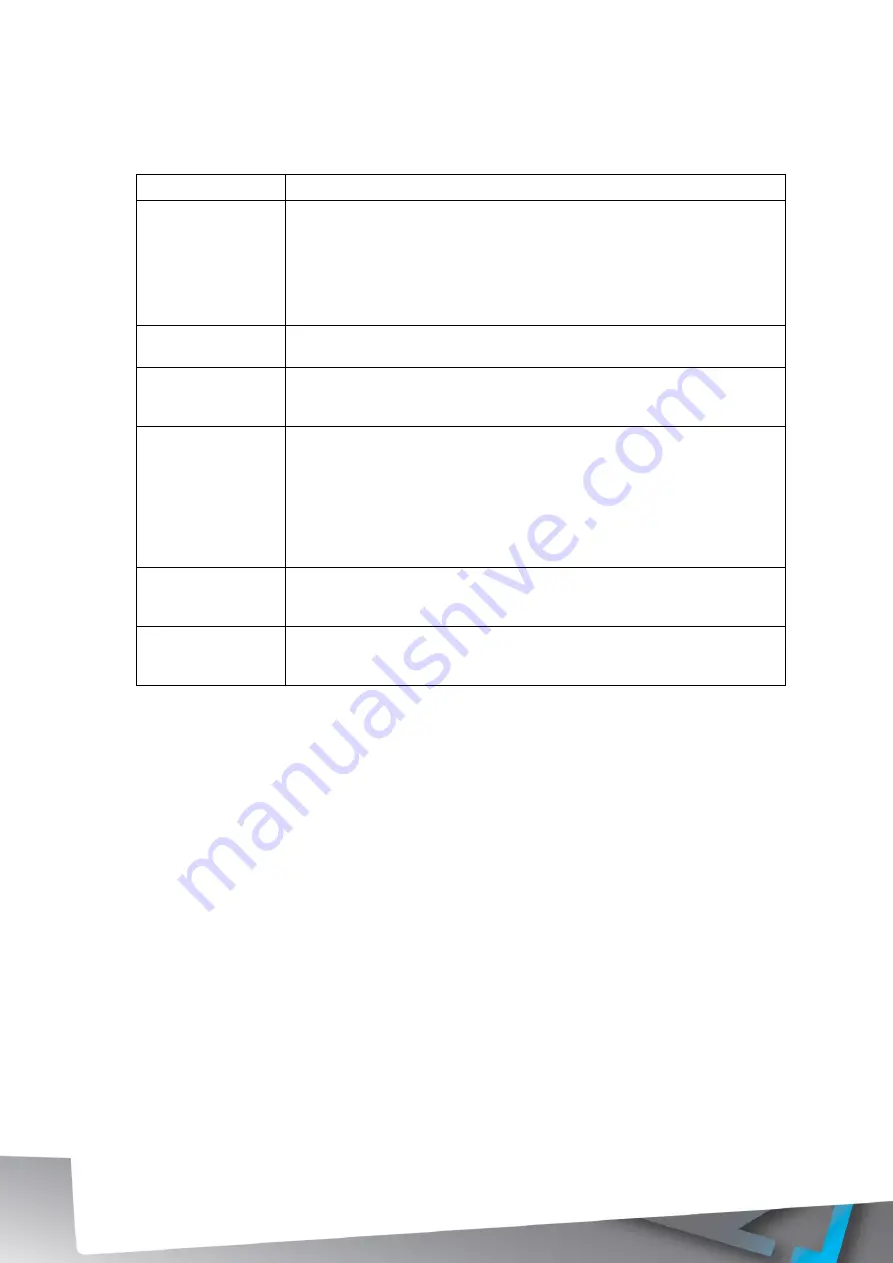

Table 3-34 Binary input signals for the impedance calculation.

Input status signal

Explanation

CURRENT_OK

The current is suitable for impedance calculation in the processed loop if, after a

zero crossing, there are three sampled values above a defined limit (~0.1In). For

a phase-ground loop calculation, it is also required that the sum of the phase

current (3Io) should be above Iphase/4. This status signal is generated within the

Z_CALC

module based on the parameter DIS21_Imin_IPar_ (I minimum) and in

case of phase-ground loops on parameters DIS21_IoBase_IPar_ (Io Base sens.)

and DIS21_IoBias_IPar_ (Io Bias)

VTS Block

Binary blocking signal due to error in the voltage measurement

VOLT_OK_HIGH

The voltage is suitable for the calculation if the most recent ten sampled values

include a sample above the defined limit (35% of the nominal loop voltage). This

status signal is generated within the

Z_CALC

module.

VOLT_OK_LOW

The voltage can be applied for the calculation of the impedance if the three most

recent sampled three values include a sample above the defined lower limit (5%

of the nominal loop voltage), but in this case the direction is to be decided using

the voltage samples stored in the memory because the secondary swings of the

capacitive voltage divider distort the sampled voltage values. Below this level,

the direction is decided based on the sign either of the real part of the

impedance or that of the imaginary part of the impedance, whichever is higher.

This status signal is generated within the

Z_CALC

module.

MEM_AVAIL

This status signal is true if the voltage memory is filled up with available samples

above the defined limit for 80 ms. This status signal is generated within the

Z_CALC

module.

HEALTHY_PHASE_

AVAIL

This status signal is true if there are healthy phase voltages (in case of

asymmetrical faults) that can be applied to directional decision. This status signal

is generated within the

Z_CALC

module.

The outputs of the scheme are calculation methods applied for impedance calculation for

the individual zones.

Содержание AQ F3 0 Series

Страница 1: ...INSTRUCTION MANUAL AQ F3x0 Feeder protection IED ...

Страница 44: ...Instruction manual AQ F3x0 Feeder protection IED 44 162 ...

Страница 84: ...Instruction manual AQ F3x0 Feeder protection IED 84 162 Figure 3 45 Polygon characteristics logic ...

Страница 148: ...Instruction manual AQ F3x0 Feeder protection IED 148 162 Figure 6 3 Panel cut out and spacing of AQ 35x IED ...

Страница 149: ...Instruction manual AQ F3x0 Feeder protection IED 149 162 Figure 6 4 Dimensions of the AQ 39x IED ...

Страница 150: ...Instruction manual AQ F3x0 Feeder protection IED 150 162 Figure 6 5 Panel cut out and spacing of the AQ 39x IED ...