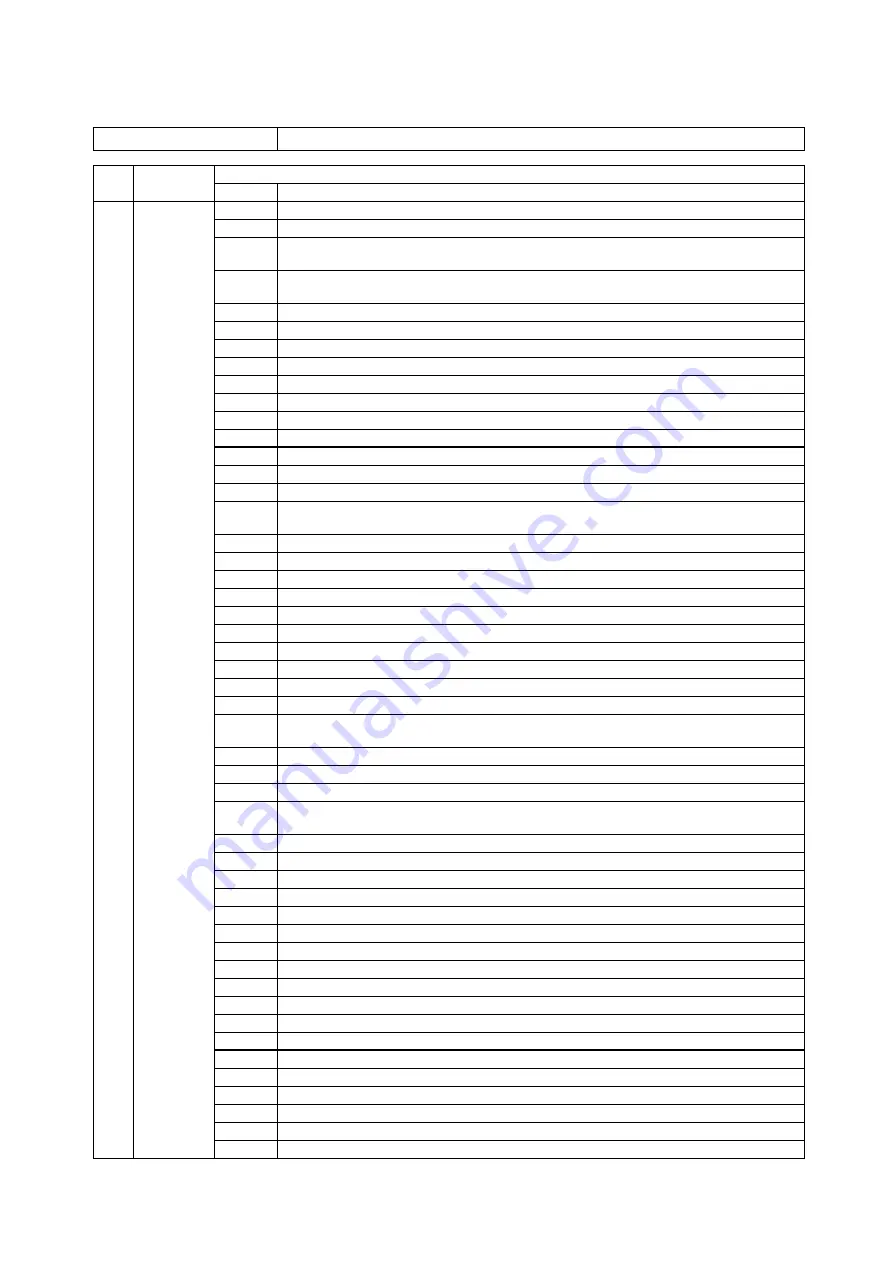

C - 4

1.10

Jul 15, 2009

250

Table 17.3 "I/O Ports" partially modified

253

17.2.3 "Timer A Count Source Select Register i (TACSi) (i = 0 to 2)" partially modified

270

Table 17.8 "Event Counter Mode Specifications (When Not Processing Two-Phase Pulse Signal)"

partially modified

274

Table 17.10 "Event Counter Mode Specifications (When Processing Two-Phase Pulse Signal with

Timers A2, A3, and A4)" partially modified

286

Figure 17.11 "Operation Example in 16-Bit Pulse Width Modulation Mode" partially modified

296

17.5.6.2 "Stop While Counting" partially modified

305

18.2.6 "Timer B Count Source Select Register i (TBCSi) (i = 0 to 3)" partially modified

315

Table 18.9 "Specifications of Pulse Period/Pulse Width Measurement Modes" note partially deleted

325

Figure 19.1 "Three-Phase Motor Control Timer Function Block Diagram 1" partially modified

347

Figure 19.6 "Usage Example of Three-Phase Mode 0 Operation" partially modified

349

Table 19.11 "Three-Phase Mode 1 Specifications" partially modified

352

Figure 19.7 "Usage Example of Three-Phase Mode 1" partially modified

356

Table 19.15 "Sawtooth Wave Modulation Mode Specifications" partially modified

359

Figure 19.9 "Usage Example of Sawtooth Wave Modulation Mode" partially modified

361

19.4.1 "Timer B2 Interrupt" partially modified

367 to 369 20.2.2 "Real-Time Clock Minute Data Register (RTCMIN)", 20.2.3 "Real-Time Clock Hour Data

Register (RTCHR)", 20.2.4 "Real-Time Clock Day Data Register (RTCWK)" partially added

370

20.2.5 "Real-Time Clock Control Register 1 (RTCCR1)" partially modified

389

20.5.4 "Time Reading Procedure of Real-Time Clock Mode" partially modified

389

Figure 20.11 "Time Data Reading" added

391

Figure 21.1 "Block Diagram of PWM" PWMCOM

→

PWMCON

396

Table 21.4 "PWM Pin and Bit Setting" partially modified

400

Figure 22.2 "Remote Control Signal Receiver Block Diagram (2/3) (PMCi Input)" partially modified

402

Table 22.3 "Registers (PMC0 Circuit)" partially modified

421

22.3.1.1 "Count Source" partially modified

422

22.3.1.2 "PMCi Input" partially added

428

22.3.2.4 "Compare Function (PMC0)" partially modified

430

Table 22.12 "Registers and Setting Values in Pattern Match Mode (Combined Operation) (1/2)"

partially modified

434

22.3.4 "Input Capture Mode (Operating PMC0 and PMC1 Individually)" partially modified

437

Figure 22.8 "Operations in Input Capture Mode" partially added

438

22.3.5 "Input Capture Mode (Simultaneous Count Operation of PMC0 and PMC1)" partially modified

439

Table 22.19 "Registers and Setting Values in Input Capture Mode (Simultaneous Count Operation)

(1/2)" partially modified

440

22.3.5.2 "Count Operation" partially modified

446 to 448 Figure 23.1 to 23.3 “Block Diagram of UART 0 to 2, and UART5 to UART7”

494

23.3.3.5 "SDA Output" 2 to 8

→

1 to 8 UiBRG count source clock cycles

496

Table 23.22 "Special Mode 2 Specifications" partially modified

510

23.5.1.2 "CLKi Output" added

24. "Serial Interface SI/O3 and SI/O4" S32C2

→

S34C2

513

Table 24.1 "SI/O3 and SI/O4 Specifications" partially modified

524

Figure 24.7 "Timing Chart for Setting SOUTi Initial Value and How to Set It" partially modified

530

Table 25.4 "Register Configuration" S11’s reset value modified

533

25.2.3 "I2C0 Address Register i (S0Di) (i = 0 to 2)" partially modified

543

Figure 25.4 "Interrupt Request Generation Timing in Receive Mode" partially modified

548

Table 25.10 "Functions Enabled by Writing to the S10 Register" partially added

561

Figure 25.11 "Start Condition Overlap Protect Function Enable Period" partially modified

565

Table 25.15 "Recommended Value of Bits SSC4 to SSC0 in Standard Clock Mode" 4.125

μ

s

→

3.3

μ

s

567

Figure 25.16 "Timeout Detection Timing" partially modified

570

25.3.10.3 "Master Reception" partially modified

576

25.5.2.4 "S3D0 Register" partially added

576

25.5.2.6 "S10 Register" partially modified

REVISION HISTORY

M16C/64A Group Hardware Manual

Rev.

Date

Description

Page

Summary

Summary of Contents for M16C/60 Series

Page 853: ...M16C 64A Group R01UH0136EJ0210...