Fusion 878A

5.0 Control Register Definitions-Function 0

PCI Video Decoder

5.3 Local Registers (Memory Mapped)

100600B

Conexant

5-35

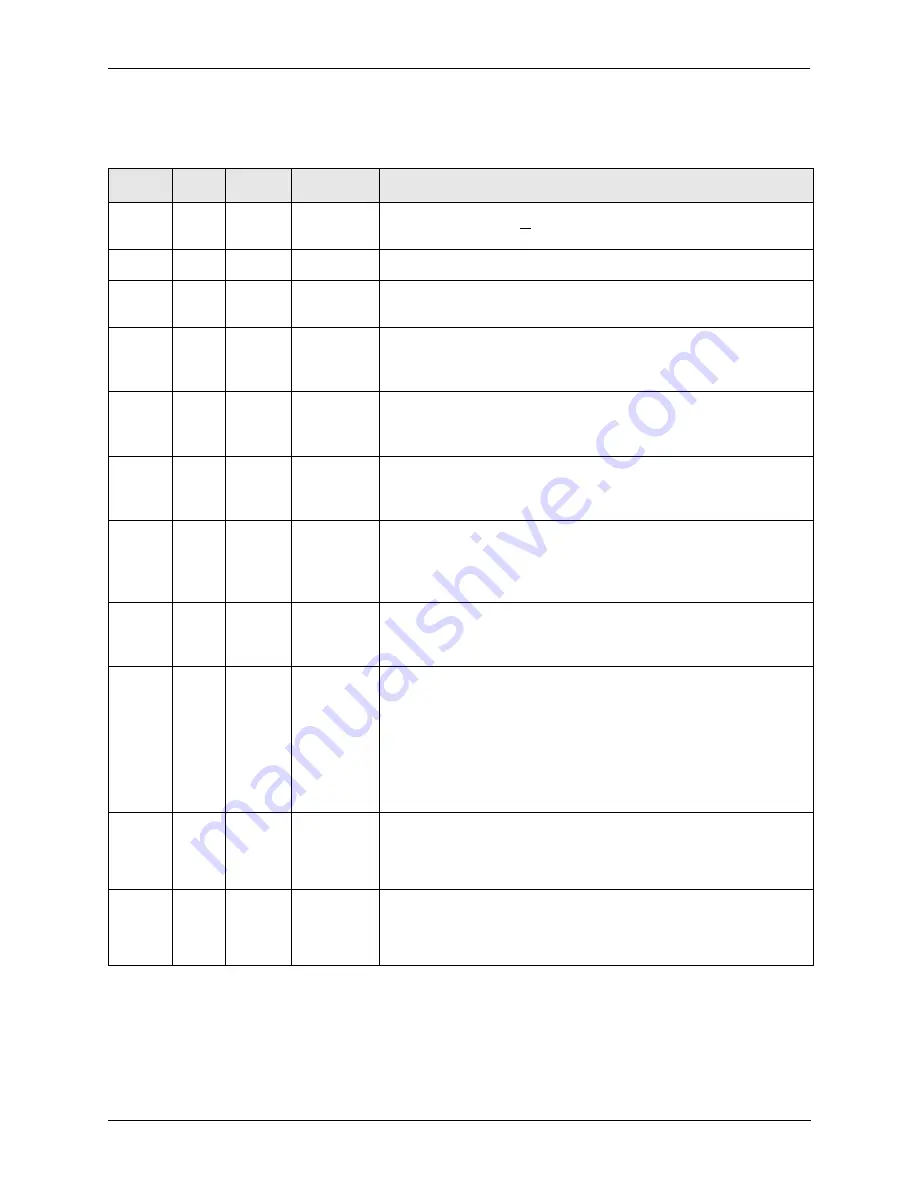

0x110—I2C Data/Control Register

Bits

Type

Default

Name

Description

[31:24]

RW

—

I2CDB0

First byte sent in an I

2

C transaction. Typically this will be the base or chip

7-bit address and the R/W bit.

[23:16]

RW

—

I2CDB1

Second byte sent in an I

2

C write transaction, usually a sub-address.

[15:8]

RW

—

I2CDB2

Third byte sent in an I

2

C write transaction, usually the data byte. After a read

transaction, this byte register will contain the data read from the slave.

[7]

RW

0

I2CMODE

I

2

C mode.

0 = Software mode

1 = Hardware mode

[6]

RW

0

I2CRATE

I

2

C timing frequency.

0 = 99.2 kHz mode

1 = 396.8 kHz mode

[5]

RW

0

I2CNOSTOP

I

2

C stop mode.

0 = Transmits stop at end of transaction

1 = Does not transmit stop at end of transaction. Holds SCL low.

[4]

RW

0

I2CNOS1B

I

2

C start mode.

0 = Transmits START or repeated START transactions. The R/W status

from bit 24 is saved for any future 1 byte transactions.

1 = Enables 1 byte read or write without START

[3]

RW

0

I2CSYNC

I

2

C synchronization.

0 = Disallows the slave to insert wait states

1 = Allows the slave to insert bit-level clock wait states

[2]

RW

0

I2CW3BRA

Number of bytes sent and master/slave acknowledge. This bit has no

meaning when I2CNOS1B (bit 4) is high during a write transaction.

0 = Writes transaction of 2 bytes I2CDB(0-1). During a 1-byte read trans-

action (I2CNOS1B is high), master sends a NACK to end the reads

from the slave.

1 = Writes transaction of 3 bytes I2CDB(0-2). During a 1-byte read trans-

action (I2CNOS1B is high), master sends an ACK after reading the

data byte.

[1]

RW

1

I2CSCL

A value of 1 releases the SCL output, and a 0 forces the SCL output low. This

bit must be set to a 1 during hardware mode. This override is for direct

software control of the bus. Reading this bit provides access to the buffered

SCL input pin.

[0]

RW

1

I2CSDA

A value of 1 releases the SDA output, and a 0 forces the SDA output low. This

bit must be set to a 1 during hardware mode. This override is for direct

software control of the bus. Reading this bit provides access to the buffered

SDA input pin.