UG-707

ADV8005 Hardware Reference Manual

spi_filter_en

, IO Map,

Address 0x1A2C[7]

This bit is used to enable the SPI anti glitch filter.

Function

spi_filter_en

Description

0 (default)

Anti glitch filter disable

1

Anti glitch filter enable

spi_filter_sel

, IO Map,

Address 0x1A2C[6]

This bit is used to select the response of the SPI anti glitch filter.

Function

spi_filter_sel

Description

0 (default)

2ns glitch rejection

1

5ns glitch rejection

4.2.8.3.

SPI Master Interface

The

SPI master interface (serial port 2) is used by the

to read the OSD binary file (output by

Blimp OSD

) from an external

SPI flash memory, and to copy it to the DDR2 memory. Note that the library of functions provided by ADI will take care of this process; the

information in this section is just provided so the user can find a suitable SPI flash memory which can be interfaced to the

SPI master

interface.

The SPI master is designed to be compatible with the M25P16 and supports the FAST_READ command. The SPI master clock can be configured

to support up to 80 MHz. The SPI master, similar to the slave, can support the following modes:

•

CPOL = 0, CPHA=0

•

CPOL = 0, CPHA=1

•

CPOL = 1, CPHA=0

•

CPOL = 1, CPHA=1

shows the effect that these settings may have on the data.

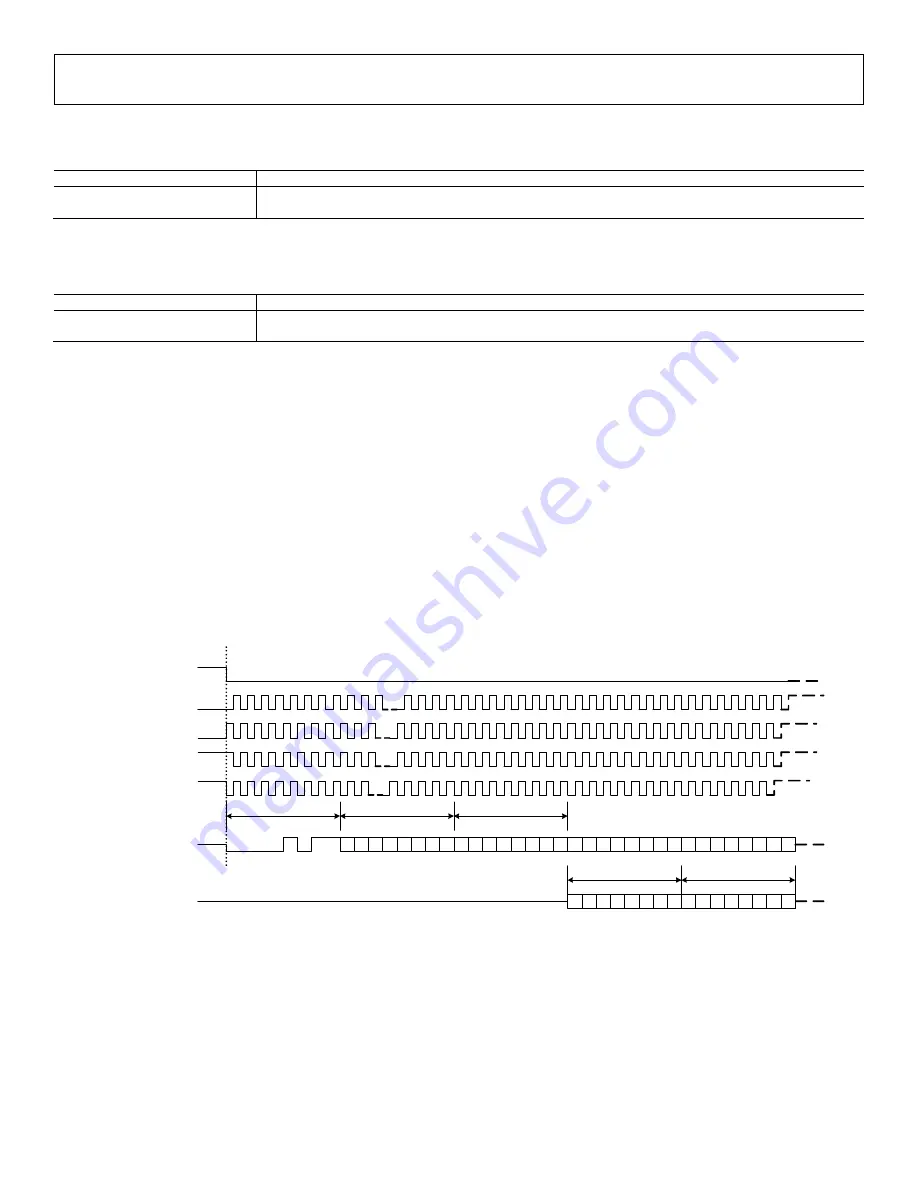

Figure 90: SPI Master Interface Timing and Data Format

23 22 21 ... 3

2

1

0

7

6

5

4

3

2

1

0

Instruction(0x0B)

24-bit Address

Dummy Byte

7

6

5

4

3

2

1

0

Data out 2

CS2

SCK2

MOSI2

MISO2

7

6

5

4

3

2

1

0

Data out 1

SCK2

SCK2

SCK2

CPOL CPHA

0

0

0

1

1

0

1

1

Rev. A | Page 180 of 317